Understanding the Differences Between PE, RIE, and ICP-RIE in Plasma Etching

By NineScrolls Engineering · 2025-01-25 · 22 min read · Materials Science

Target Readers: Semiconductor process engineers, equipment engineers, R&D scientists, and technical decision-makers in plasma processing.

TL;DR Summary

Plasma etching technologies range from simple chemical dry etching (often called PE) to advanced Reactive Ion Etching (RIE) and Inductively Coupled Plasma RIE (ICP-RIE). PE relies on chemical radicals for isotropic etching at 100–300 nm/min; RIE adds ion bombardment for anisotropic profiles at 200–500 nm/min; ICP-RIE provides independent control of plasma density (1011–1012 cm−3) and ion energy, achieving etch rates above 1 µm/min with excellent profile control. This article covers working principles, gas chemistries, typical process parameters, the Bosch process for DRIE, common etch defects and solutions, and endpoint detection methods — everything you need to select and optimize the right technology for your application.

1. Terminology: What Does "PE" Actually Mean?

Before comparing technologies, it is important to clarify terminology. "PE" (Plasma Etching) is a general term that encompasses all plasma-based etching methods. However, in comparative literature it is often used as shorthand for chemical dry etching — the simplest plasma etching mode where material removal is driven almost entirely by chemical reactions with minimal ion bombardment. This mode is also known as barrel etching, downstream etching, or radical etching, depending on the reactor configuration.

In this article, we use "PE" specifically to refer to this chemistry-dominated, isotropic etching mode, as distinct from the ion-assisted mechanisms of RIE and ICP-RIE. For a broader introduction to plasma etching fundamentals, see our Plasma Etching Fundamentals guide.

2. Plasma Etching (PE) — The Foundation

PE is the most basic form of plasma etching. The substrate sits on or near a grounded electrode (or downstream from the plasma source), so ions reach the surface with very low energy. Material removal is dominated by volatile reaction products formed when reactive radicals — F*, Cl*, O* — react with the substrate surface.

How PE Works

- Chemical Dominance: Reactive radicals (F*, Cl*, O*) react chemically with the substrate. Ion energy is typically < 20 eV, far below the physical sputtering threshold.

- Isotropic Nature: Because radicals have no preferred direction, etching proceeds equally in all directions — producing rounded, undercut profiles.

- High Selectivity: Purely chemical etching can achieve selectivities of 50:1 or higher for certain material pairs (e.g., Si over SiO₂ in CF₄/O₂).

- Minimal Damage: Low ion energy means negligible lattice damage — important for sensitive III-V devices and organic materials.

Typical PE Process Parameters

| Parameter | Typical Range |

|---|---|

| Etch Rate | 100–300 nm/min |

| Chamber Pressure | 300–1000 mTorr |

| RF Power | 100–300 W |

| Substrate Temperature | 20–80 °C |

| Plasma Density | 109–1010 cm−3 |

Common PE Gas Chemistries

| Material | Gas Chemistry | Notes |

|---|---|---|

| Photoresist | O₂ | Ashing/stripping; 200–500 nm/min |

| Silicon | CF₄, SF₆ | Isotropic; high selectivity to SiO₂ |

| SiO₂ | CF₄/O₂ | Moderate rate; widely available |

| Organics | O₂/Ar | Surface cleaning and activation |

PE Applications

- Photoresist stripping and ashing

- Surface preparation and activation before bonding or deposition

- Isotropic release etching for MEMS structures

- Descum and residue removal

Figure 1: Etch Profile Comparison — Isotropic (PE/wet etch), Anisotropic (RIE), and High Aspect Ratio (ICP-RIE/DRIE) profiles through film layers

3. Reactive Ion Etching (RIE) — The Evolution

RIE overcomes PE's fundamental limitation — the lack of directional control. In a capacitively coupled plasma (CCP) reactor, the substrate sits on the powered electrode, developing a DC self-bias that accelerates ions perpendicular to the surface. This dual mechanism of chemical reaction plus physical ion bombardment produces anisotropic etch profiles that are essential for pattern transfer in semiconductor fabrication.

How RIE Differs from PE

- Ion-Enhanced Etching: Energetic ions (50–500 eV) break surface bonds, enabling chemical reactions that would not occur spontaneously — the ion-neutral synergy effect first demonstrated by Coburn and Winters.

- Directional Profiles: Vertical ion bombardment clears the trench bottom faster than radicals attack sidewalls, producing anisotropic profiles with sidewall angles of 80–90°.

- Coupled Parameters: In a single-RF CCP system, plasma density and ion energy are not independently controllable — increasing RF power raises both simultaneously. This is the key limitation RIE inherits from its architecture.

- Lower Pressure Operation: RIE typically operates at 10–200 mTorr (vs. 300–1000 mTorr for PE), increasing ion mean free path and directionality.

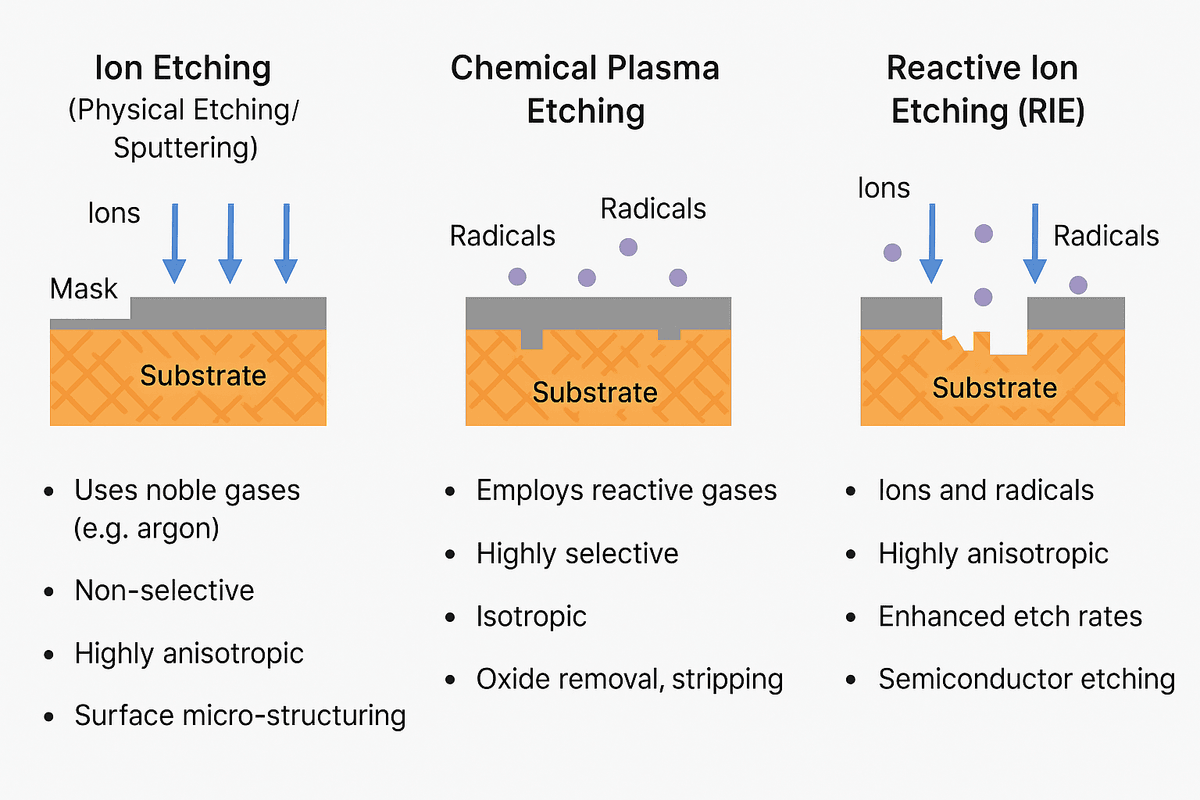

Figure 2: PE/RIE/ICP-RIE Reactor Architectures — chamber cross-sections and resulting etch profiles

Typical RIE Process Parameters

| Parameter | Typical Range |

|---|---|

| Etch Rate | 200–500 nm/min |

| Chamber Pressure | 10–200 mTorr |

| RF Power | 100–600 W (13.56 MHz) |

| DC Self-Bias | −100 to −500 V |

| Substrate Temperature | 20–100 °C |

| Plasma Density | 1010–1011 cm−3 |

Common RIE Gas Chemistries

| Material | Gas Chemistry | Notes |

|---|---|---|

| Silicon | SF₆, CF₄/O₂, Cl₂/HBr | SF₆ for fast isotropic; Cl₂/HBr for anisotropic |

| SiO₂ | CHF₃, C₄F₈, CF₄/CHF₃ | Fluorocarbon polymer sidewall passivation |

| Si₃N₄ | CHF₃/O₂, CF₄/H₂ | H₂ addition improves selectivity to SiO₂ |

| Al | Cl₂/BCl₃ | BCl₃ scavenges native oxide |

| GaAs / InP | Cl₂/Ar, SiCl₄ | Requires careful temperature control |

RIE Applications

- Pattern transfer for semiconductor device fabrication

- Dielectric and metal etching

- MEMS device fabrication (moderate aspect ratios)

- Optical waveguide definition

For a comprehensive deep dive into RIE principles and process optimization, see our Reactive Ion Etching Guide.

4. Inductively Coupled Plasma RIE (ICP-RIE) — The Advanced Solution

ICP-RIE solves the fundamental limitation of conventional RIE by decoupling plasma generation from ion energy control. An external ICP coil (powered at 13.56 MHz or 2 MHz) generates a high-density plasma through inductive coupling, while a separate RF bias on the substrate electrode independently controls ion energy. This dual-source architecture enables process windows that are simply impossible with single-RF RIE.

ICP-RIE Architecture Advantages

- Dual RF System: ICP source (300–3000 W) for plasma density + RF bias (0–600 W) for ion energy — each tunable independently.

- High-Density Plasma: Plasma densities of 1011–1012 cm−3 — 10–100× higher than CCP-based RIE.

- Low-Pressure Operation: Stable plasma at 1–50 mTorr enables long ion mean free paths and highly anisotropic etching.

- Decoupled Control: High etch rate with low damage (high density, low bias) or high aspect ratio with controlled passivation — simultaneously optimizable.

Figure 3: Reactor Architecture Comparison — PE (Chemical Dry Etch) uses grounded electrodes with low-density plasma; RIE (CCP) adds RF bias for directional etching; ICP-RIE decouples plasma density and ion energy via an inductive coil + separate bias electrode

Typical ICP-RIE Process Parameters

| Parameter | Typical Range |

|---|---|

| Etch Rate | 500–5000+ nm/min (material-dependent) |

| Chamber Pressure | 1–50 mTorr |

| ICP Source Power | 300–3000 W |

| RF Bias Power | 0–600 W |

| DC Self-Bias | 0 to −300 V (independently controlled) |

| Substrate Temperature | −20 to 200 °C (cryogenic to heated) |

| Plasma Density | 1011–1012 cm−3 |

The Bosch Process: Deep Reactive Ion Etching (DRIE)

The Bosch process (patented by Robert Bosch GmbH, 1994) is an ICP-RIE technique that alternates between two steps to achieve deep, high-aspect-ratio features in silicon:

- Etch Step: SF₆ plasma isotropically etches silicon at high rates (3–10 µm/min).

- Passivation Step: C₄F₈ plasma deposits a thin fluorocarbon polymer on all surfaces (sidewalls and trench bottom).

During the next etch step, ion bombardment preferentially removes the polymer from the trench bottom (directional), while the sidewall polymer remains intact (no direct ion bombardment). This cyclic process produces near-vertical sidewalls with aspect ratios exceeding 50:1, though characteristic scalloping (sidewall roughness of 50–200 nm per cycle) is visible at high magnification.

For a detailed discussion of DRIE process optimization and scallop reduction, see our dedicated Bosch Process Guide. For a comparison with cryogenic etching approaches, see Cryogenic Etching vs. Bosch Process.

ICP-RIE Applications

- Deep silicon etching for MEMS and TSV (through-silicon via)

- Advanced semiconductor device fabrication (FinFET, gate etch)

- III-V compound semiconductor etching (GaN, SiC, GaAs)

- Photonic crystal and optical device manufacturing

- Quantum device fabrication (superconducting qubits, diamond NV centers)

For more on ICP-RIE capabilities, see our ICP-RIE Technology article.

5. Technology Comparison Matrix

The following table consolidates the key differences across all three technologies with quantitative values where possible:

| Feature | PE (Chemical Dry Etch) | RIE (CCP) | ICP-RIE |

|---|---|---|---|

| Plasma Density | 109–1010 cm−3 | 1010–1011 cm−3 | 1011–1012 cm−3 |

| Ion Energy | < 20 eV | 50–500 eV | 0–300 eV (independent) |

| Typical Etch Rate (Si) | 100–300 nm/min | 200–500 nm/min | 500–5000+ nm/min |

| Operating Pressure | 300–1000 mTorr | 10–200 mTorr | 1–50 mTorr |

| Profile Control | Isotropic | Anisotropic (80–90°) | Highly Anisotropic (88–90°) |

| Selectivity | Very High (> 50:1) | Moderate (10–30:1) | High (20–100:1, tunable) |

| Max Aspect Ratio | N/A (isotropic) | 5–10:1 | 50:1+ (Bosch process) |

| Surface Damage | Minimal | Moderate | Low–Moderate (controllable) |

| Parameter Coupling | N/A | Density & energy coupled | Density & energy independent |

| Equipment Cost | Low ($50K–$150K) | Medium ($100K–$300K) | High ($200K–$600K+) |

6. Common Etching Challenges and Solutions

Regardless of which technology you use, certain etch defects can arise. Understanding these failure modes and their root causes is essential for process optimization.

Undercut

Problem: Lateral etching beneath the mask, resulting in loss of critical dimension (CD) control.

Causes: Excessive chemical etching component; high pressure; insufficient sidewall passivation.

Solutions: Reduce pressure to increase ion directionality; add passivation gas (C₄F₈, CHF₃); increase RF bias; switch from PE to RIE or ICP-RIE for better anisotropy.

Bowing

Problem: Convex bulging of trench sidewalls, particularly in deep features.

Causes: Ion scattering off the mask edge or upper sidewall; charge buildup deflecting ions.

Solutions: Optimize mask profile (tapered vs. vertical); reduce chamber pressure; use pulsed bias to reduce charging effects; adjust Bosch cycle timing.

Aspect Ratio Dependent Etching (ARDE)

Problem: Etch rate decreases as feature aspect ratio increases — narrow trenches etch slower than wide ones on the same wafer.

Causes: Knudsen transport limitation of neutrals into high-aspect-ratio features; ion shadowing at trench entrance.

Solutions: Increase ICP power to raise radical flux; reduce pressure for longer mean free path; use time-multiplexed recipes with longer etch cycles for deep features. See our article on achieving ultra-high etch selectivity for related strategies.

Micro-masking and Grass Formation

Problem: Needle-like or grass-like residues on the etch surface, caused by micro-scale masking from redeposited material or contaminants.

Causes: Metal contamination (from chamber walls or mask material); incomplete polymer removal during Bosch cycles; native oxide residues.

Solutions: Chamber conditioning and cleaning; add O₂ to remove polymer residues; use oxide-free starting surfaces; optimize Bosch passivation/etch ratio.

Notching (Footing)

Problem: Lateral etching at the interface of silicon and an underlying insulator (e.g., SOI buried oxide).

Causes: Charge accumulation on the insulating surface deflects ions sideways.

Solutions: Use pulsed bias or pulsed plasma to allow charge dissipation; reduce bias power near endpoint; apply backside helium cooling.

For a broader discussion of plasma non-uniformity challenges, see Why Plasma Is Non-Uniform in Etch Chambers.

7. Endpoint Detection Methods

Knowing exactly when to stop etching is critical for yield and device performance. Three primary methods are used across PE, RIE, and ICP-RIE systems:

| Method | Principle | Best For | Limitations |

|---|---|---|---|

| Optical Emission Spectroscopy (OES) | Monitors emission wavelengths of reactive species and etch byproducts in the plasma. A change in intensity signals the transition between materials. | All plasma etch systems; most widely used; non-invasive | Requires sufficient exposed area (> 1–5% of wafer); signal can be weak for small open areas |

| Laser Interferometry | A laser beam reflects off the film being etched. Constructive/destructive interference fringes track film thickness in real time. | Transparent films (SiO₂, Si₃N₄); precise thickness control; works for small areas | Requires optically transparent film; not suitable for metals or opaque materials |

| Mass Spectrometry (RGA) | Residual gas analyzer samples exhaust gases, detecting etch byproduct species (e.g., SiF₄ during Si etching). | High sensitivity for trace materials; process debugging and characterization | Slower response time; higher equipment cost; more common in R&D than production |

8. Selection Guidelines

Choose PE When:

- Isotropic etching is acceptable or desired (e.g., release etching, undercutting for liftoff)

- Maximum selectivity is needed and profile control is not critical

- Minimal surface damage is required (sensitive devices, III-V materials)

- Photoresist stripping, descum, or surface cleaning applications

- Budget is constrained and process requirements are straightforward

Choose RIE When:

- Anisotropic pattern transfer is needed with moderate aspect ratios (< 10:1)

- Standard semiconductor processing: gate etch, contact etch, dielectric etch

- Metal etching (Al, Ti, Cr) where moderate ion energy is sufficient

- Cost-effective solution — when the process window does not require independent density/energy control

- Lab environments with lower throughput requirements

Choose ICP-RIE When:

- High-aspect-ratio features are required (> 10:1, up to 50:1+)

- Independent control of etch rate and ion energy is needed (e.g., high rate + low damage)

- Deep silicon etching (DRIE / Bosch process) for MEMS or TSV

- Hard-to-etch materials: GaN, SiC, diamond, sapphire, III-V compounds

- Advanced R&D requiring maximum process flexibility

For guidance on selecting the right system for your lab, see our Semiconductor Etcher Selection Guide.

Figure 5: Quantitative Comparison Matrix — Key performance parameters across PE, RIE, and ICP-RIE technologies

9. Frequently Asked Questions

What is the main difference between RIE and ICP-RIE?

The fundamental difference is parameter coupling. In RIE (a capacitively coupled plasma system), plasma density and ion energy are controlled by a single RF source — increasing power raises both simultaneously. ICP-RIE uses two separate RF sources: an ICP coil for plasma generation and an independent RF bias for ion energy. This decoupled architecture allows you to achieve high etch rates (from high plasma density) with low damage (from low bias power) — a combination that is impossible in conventional RIE.

When should I use the Bosch process instead of continuous etching?

The Bosch (time-multiplexed) process is preferred when you need deep, high-aspect-ratio features in silicon (typically > 10 µm depth and > 10:1 aspect ratio). Continuous etching with simultaneous etch/passivation gases (e.g., SF₆/C₄F₈ mixed) produces smoother sidewalls but is limited to lower aspect ratios. If sidewall scalloping is unacceptable (e.g., for optical applications), consider cryogenic etching as an alternative.

What gases are most commonly used in plasma etching?

The choice depends on the target material: SF₆ and CF₄ for silicon; CHF₃ and C₄F₈ for SiO₂ and Si₃N₄; Cl₂/BCl₃ for metals (Al) and III-V semiconductors; O₂ for photoresist stripping and organic materials. Additives like Ar improve bombardment, while O₂ or H₂ tune selectivity by modifying the fluorocarbon polymer chemistry.

How do I reduce etch damage to sensitive devices?

Use ICP-RIE with low RF bias power (or zero bias for purely chemical etching at high density). Pulsed plasma techniques — where RF power is modulated at 1–10 kHz — can further reduce ion energy spread and charge-induced damage. For the most damage-sensitive applications (quantum devices, photonic crystals), downstream PE may be appropriate. See our article on Atomic Layer Etching for the ultimate in damage-free processing.

Can I etch multiple materials in one chamber?

Yes, with proper gas and process switching. ICP-RIE systems with multiple mass flow controllers (typically 4–8 gas lines) and automated recipe management can handle silicon, dielectrics, metals, and III-V materials. Cross-contamination can be managed with chamber conditioning steps between processes. NineScrolls systems support multiple process design kits for this purpose.

10. NineScrolls Plasma Etching Solutions

NineScrolls designs plasma etching systems specifically for the challenges discussed in this article — from basic RIE pattern transfer to advanced ICP-RIE deep etching.

RIE Etcher Series

Optimized for standard RIE applications where cost-effectiveness and reliability matter:

- Compact design (1.0 m × 1.0 m footprint) for cleanroom space efficiency

- 13.56 MHz RF source with automatic matching for stable plasma ignition

- Up to 4 gas lines with precision mass flow controllers

- Real-time process monitoring (pressure, power, DC bias)

- Suitable for Si, SiO₂, Si₃N₄, metal etching, and photoresist stripping

ICP Etcher Series

Designed for researchers and process engineers who need independent parameter control and high-density plasma:

- Uni-body design (1.0 m × 1.5 m footprint) with integrated ICP source and RF bias

- ICP source up to 3000 W + independent RF bias up to 600 W

- Plasma density up to 1012 cm−3 for high etch rates

- Substrate temperature control from −20 °C to 200 °C (He backside cooling)

- Up to 8 gas lines for complex multi-step recipes (Bosch process ready)

- Process design kits available for: Si DRIE, SiO₂, GaN/SiC, III-V, and diamond

- Laser interferometry endpoint detection (optional OES)

Figure 4: Etching Capabilities Comparison — PE, RIE, and ICP-RIE performance characteristics

11. Future Trends in Plasma Etching

- Atomic Layer Etching (ALE): Self-limiting, monolayer-precision removal — the etch analog of ALD. Increasingly critical for sub-5 nm node processing. See our ALE Practical Guide.

- Pulsed Plasma Etching: Modulating plasma source and/or bias at kHz frequencies narrows ion energy distribution, reducing damage while maintaining etch rate.

- Machine Learning Process Control: AI-driven run-to-run and real-time optimization using OES, impedance, and sensor data for predictive process control and virtual metrology. See our article on ML for Plasma Etch Optimization.

- New Material Challenges: Etching emerging materials (2D materials, high-entropy alloys, ferroelectric HfO₂) requires entirely new gas chemistries and process approaches. See Etching Beyond Silicon.

- 3D Integration: Advanced etching for through-silicon vias (TSV), hybrid bonding, and chiplet packaging — driving demand for deeper, higher-aspect-ratio features with tighter CD control.

12. Conclusion

The choice between PE, RIE, and ICP-RIE ultimately depends on three factors: required anisotropy, process flexibility, and budget. PE (chemical dry etching) offers the simplest, lowest-damage approach for isotropic applications. RIE introduces directional control for mainstream pattern transfer at moderate cost. ICP-RIE provides the highest performance and process flexibility — independent density and energy control, support for the Bosch process, and compatibility with the widest range of materials — making it the technology of choice for advanced research and high-aspect-ratio fabrication.

Understanding the physics, trade-offs, and failure modes of each technology enables process engineers to make informed equipment decisions and optimize etch recipes more efficiently.

Get Started with the Right Etching Solution

- Need help selecting a technology? Our process engineers can evaluate your application requirements and recommend the optimal system configuration. Contact our technical team.

- Explore our systems: RIE Etcher | ICP Etcher | Striper Systems

- Request a process evaluation: Send us your material stack and target specifications — we will provide a recommended recipe and system configuration at no cost.

References

- Lieberman, M. A. & Lichtenberg, A. J. Principles of Plasma Discharges and Materials Processing, 2nd ed. Wiley-Interscience (2005). ISBN 978-0471720010.

- Coburn, J. W. & Winters, H. F. "Plasma etching — A discussion of mechanisms." Journal of Vacuum Science & Technology, 16(2), 391–403 (1979). doi:10.1116/1.569958

- Hopwood, J. "Review of inductively coupled plasmas for plasma processing." Plasma Sources Science and Technology, 1(2), 109 (1992). doi:10.1088/0963-0252/1/2/006

- Laermer, F. & Schilp, A. "Method of anisotropically etching silicon." U.S. Patent 5,501,893 (1996). (The Bosch Process patent.)

- Jansen, H. V. et al. "A survey on the reactive ion etching of silicon in microtechnology." Journal of Micromechanics and Microengineering, 6(1), 14–28 (1996). doi:10.1088/0960-1317/6/1/002

- Wu, B. et al. "High aspect ratio silicon etch: A review." Journal of Applied Physics, 108(5), 051101 (2010). doi:10.1063/1.3474652

- Donnelly, V. M. & Kornblit, A. "Plasma etching: Yesterday, today, and tomorrow." Journal of Vacuum Science & Technology A, 31(5), 050825 (2013). doi:10.1116/1.4819316

- Lee, C. G. N. et al. "Etching of SiC using inductively coupled SF₆/O₂ plasma." Journal of The Electrochemical Society, 151(2), G81–G87 (2004). doi:10.1149/1.1636740

- Kanarik, K. J. et al. "Overview of atomic layer etching in the semiconductor industry." Journal of Vacuum Science & Technology A, 33(2), 020802 (2015). doi:10.1116/1.4913379

- Rangelow, I. W. "Critical tasks in high aspect ratio silicon dry etching for microelectromechanical systems." Journal of Vacuum Science & Technology A, 21(4), 1550–1562 (2003). doi:10.1116/1.1580488

- Madou, M. J. Fundamentals of Microfabrication and Nanotechnology, 3rd ed. CRC Press (2011). ISBN 978-0849331800.

- Huang, S. et al. "Plasma etching of high aspect ratio features in SiO₂ using Ar/C₄F₈/O₂ mixtures: A computational investigation." Journal of Vacuum Science & Technology A, 37(3), 031304 (2019). doi:10.1116/1.5090606

- Ishikawa, K. et al. "Progress and prospects in nanoscale dry processes: How can we control atomic-scale reactions?" Japanese Journal of Applied Physics, 56(6S2), 06HA02 (2017). doi:10.7567/JJAP.56.06HA02