The Selectivity Challenge: Achieving Ultra-High Etch Selectivity in Modern Plasma Processes

By NineScrolls Engineering · 2026-02-25 · 22 min read · Materials Science

Target Readers: Process engineers, researchers, and technical decision-makers developing high-selectivity plasma etch processes. This guide covers the fundamentals of etch selectivity, practical strategies for improvement, detailed case studies with quantitative results, and emerging trends driving selectivity requirements beyond 100:1.

Introduction

In an ideal world, a plasma etch process would remove exactly the material you want — and absolutely nothing else. In reality, every etch process attacks surrounding materials to some degree. The ratio of how fast you etch the target material versus how fast you etch the material you want to preserve is called etch selectivity, and it is one of the most critical — and most challenging — parameters in plasma process development.

As device structures become more complex, the demands on etch selectivity are escalating. Advanced logic devices feature multiple thin film layers stacked in close proximity. 3D NAND structures require etching through dozens of alternating layers. Gate-all-around (GAA) transistors demand selective removal of one material from a nanoscale sandwich while preserving neighboring layers that are just a few nanometers thick.

This article explores why selectivity is becoming the defining challenge of modern plasma etching, the physical and chemical mechanisms that control it, practical strategies for achieving the selectivity your research demands, and emerging trends in selectivity-driven process design.

Understanding Etch Selectivity

Definition and Metrics

Etch selectivity is defined as:

Selectivity = Etch Rate of Target Material / Etch Rate of Material to Preserve

A selectivity of 10:1 means the target material etches 10 times faster than the material you want to keep. For many research applications, selectivities of 10:1 to 50:1 are sufficient. But advanced semiconductor manufacturing increasingly demands selectivities of 100:1, 500:1, or even “infinite” (where the stop layer is essentially not etched at all).

Why Selectivity Matters More Than Ever

Consider these scaling trends:

Thinner layers: As etch-stop and barrier layers thin from 10 nm to 2 nm, even a selectivity of 50:1 means you consume 0.4 nm of the stop layer during an over-etch — 20% of its total thickness. At these dimensions, selectivities of 200:1 or higher are needed to maintain acceptable process margins.

3D architectures: In 3D NAND, the etch must penetrate through 100+ alternating layers of SiO₂ and Si₃N₄ (or polysilicon) to create channel holes with aspect ratios exceeding 60:1. The selectivity between the alternating layers directly determines the electrical performance of every cell.

Self-aligned processes: Modern patterning relies on self-aligned etch steps where selectivity between different materials replaces lithographic alignment. If selectivity is insufficient, the self-alignment advantage is lost.

Damage budgets: Even when selectivity ratios look acceptable on paper, the physical and chemical damage to preserved layers during the etch can be more problematic than the material loss itself. True “selectivity” must account for both removal rate and damage.

The Physics and Chemistry of Selectivity

Etch selectivity is fundamentally determined by the differences in how two materials interact with the plasma environment. Understanding these mechanisms is the key to engineering higher selectivity.

Chemical Selectivity

Chemical selectivity arises from differences in the volatility of etch products. If the target material forms volatile products with the reactive gas while the stop material forms involatile products, chemical selectivity can be very high.

Classic examples include:

- Si over SiO₂ in fluorine plasmas: By tuning conditions to favor fluorine-deficient, polymer-depositing plasmas, SiO₂ etch is suppressed while Si continues to etch. Selectivities > 100:1 are achievable.

- Si₃N₄ over SiO₂ in hydrofluorocarbon plasmas: H₂-containing fluorocarbon gases (e.g., CH₃F, CH₂F₂) deposit a carbon-rich polymer on SiO₂ surfaces that inhibits etching, while the nitrogen in Si₃N₄ prevents polymer accumulation. This “etch/deposition competition” mechanism enables very high selectivity.

- Cl₂-based etching of Al over SiO₂: AlCl₃ is volatile while SiCl₄ formation is slow on oxide surfaces, providing natural chemical selectivity.

Ion-Energy-Dependent Selectivity

Many selective etch processes exploit differences in the ion energy threshold for etching different materials. Below a certain ion energy, a material may not etch at all (or only at negligible rates), while the target material etches readily.

This is the fundamental mechanism behind atomic layer etching selectivity: the modification step alters only the target material, and the low-energy removal step is tuned to remove the modified layer while leaving the unmodified stop layer intact.

The key implication for equipment is clear: precise, independent control of ion energy (through bias power) at low values (10–100 eV) is essential for ion-energy-driven selectivity.

Passivation-Based Selectivity

In many processes, selectivity is achieved not by inherent chemical differences but by engineering a passivation layer on the material to be preserved. This passivation blocks further etching while the target material continues to be removed.

Polymer deposition from fluorocarbon gases is the most common example. By tuning the balance between etch and deposition through gas composition, pressure, and ion energy, selective passivation of the stop layer can be achieved.

Temperature-Dependent Selectivity

Etch selectivity often has a strong temperature dependence because different materials have different activation energies for surface reactions. In some cases, lowering the substrate temperature dramatically increases selectivity by suppressing the etch of the stop layer while maintaining a reasonable rate for the target material. This is one reason why cryogenic etching can achieve exceptional selectivities in certain material systems.

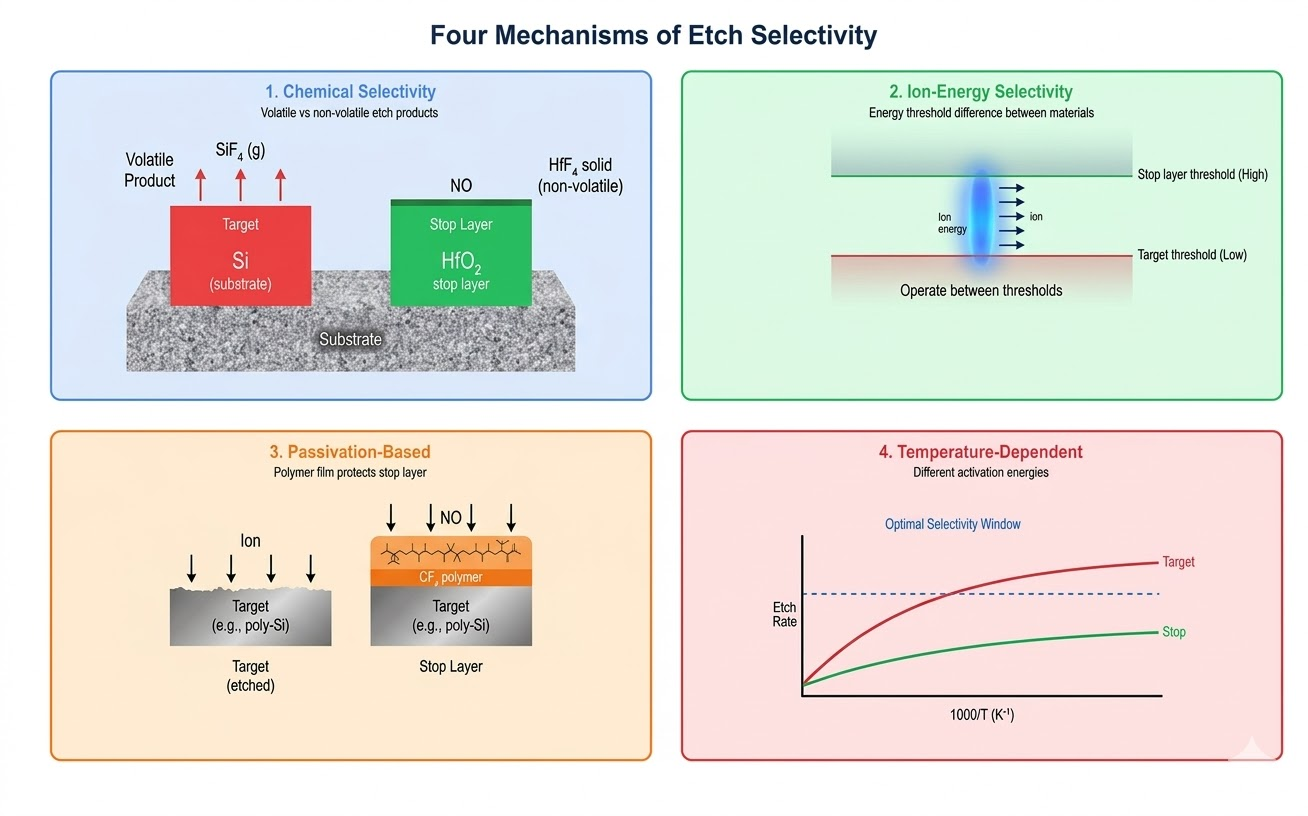

Figure 1: Etch Selectivity Mechanisms — four fundamental mechanisms controlling selectivity in plasma processes

Practical Strategies for Improving Selectivity

Strategy 1: Optimize Gas Chemistry

The first and most powerful lever for selectivity is gas composition. Key principles:

- Add hydrogen to fluorocarbon gases to increase polymer deposition and enhance oxide selectivity. Moving from CF₄ to CHF₃ to CH₂F₂ to CH₃F progressively increases carbon-to-fluorine ratio and polymer deposition rate.

- Add oxygen to remove deposited polymer when it is suppressing etching of the target material. O₂ addition can tune the etch/deposition balance.

- Use gas mixtures that form volatile products with the target but involatile products with the stop layer.

- Consider additive gases like N₂, CO, or COS that can modify surface chemistry and polymer composition for finer selectivity tuning.

Strategy 2: Reduce Ion Energy

Lower bias power reduces the physical sputtering component of etching, allowing chemical selectivity to dominate. In ICP-RIE systems, the ability to set very low bias power (5–50 W) while maintaining high ICP power (for radical generation) is the hardware enabler for this approach. This independent source/bias architecture is essential for high-selectivity processes.

Strategy 3: Increase Pressure

Higher process pressure increases the radical-to-ion flux ratio, shifting the etch mechanism toward chemical etching and away from physical sputtering. The sweet spot for high-selectivity ICP-RIE processes is typically 10–50 mTorr: high enough for good radical density and selectivity, low enough for adequate anisotropy.

Strategy 4: Pulsed Plasma

Pulsing the plasma (alternating between on and off states at frequencies of 100 Hz to 10 kHz) is a powerful technique for enhancing selectivity. During the plasma-off phase:

- Reactive radicals continue to etch (chemical component), but ion bombardment stops

- Polymer deposition from residual radicals can passivate the stop layer

- Charged species recombine, reducing damage

Pulsed ICP and pulsed bias approaches have demonstrated significant selectivity improvements in multiple material systems.

Strategy 5: Leverage ALE

For the ultimate in selectivity, atomic layer etching provides a fundamentally different approach. Because the surface modification step is self-limiting and material-specific, ALE can achieve effectively infinite selectivity when the stop material does not react with the modification chemistry. See our article on Atomic Layer Etching for Semiconductor Manufacturing for detailed discussion of ALE mechanisms and selectivity.

Strategy 6: Temperature Tuning

Explore substrate temperature as a selectivity lever:

- Cooling (down to cryogenic temperatures) can freeze out reactions on the stop layer while the target still etches via ion-assisted mechanisms

- Heating (50–300°C) can improve byproduct volatility for certain materials, enabling lower ion energies and thus better selectivity

Strategy 7: Multi-Step and Hybrid Etch Approaches

For the most demanding selectivity requirements, single-step processes often cannot deliver. Multi-step approaches combine different etch mechanisms sequentially:

- Bulk etch + finishing etch: Use a fast, moderate-selectivity process for 80–90% of the target removal, then switch to a slow, high-selectivity process for the final landing on the stop layer.

- Plasma etch + wet clean: A hybrid approach where plasma etching provides anisotropic profile control, followed by a brief wet dip (dilute HF, HCl, or TMAH) to remove residual damage.

- ALE finishing: After conventional ICP-RIE removes most of the target material, switch to ALE mode for the final 5–10 nm. This provides effectively infinite selectivity at the stop layer while maintaining throughput for bulk removal.

Case Study — Two-Step Gate Recess for GaN HEMTs

A production-oriented process uses: Step 1 — Cl₂/BCl₃ ICP-RIE at 100 V bias (etch rate: 65 nm/min, selectivity to AlGaN: 15:1) to remove 80% of the GaN cap; Step 2 — Cl₂/Ar at 15 V bias (etch rate: 8 nm/min, selectivity: 80:1) for the final 20% landing. The two-step approach achieves an effective process selectivity of > 50:1 with 3× the throughput of a single low-bias step. Vth uniformity across the 6-inch wafer improved from ±0.15 V (single-step) to ±0.05 V (two-step).

Case Studies in High-Selectivity Etching

Case Study 1: Si₃N₄ over SiO₂ for 3D NAND Replacement Gate

Chemistry: CH₃F/O₂/Ar (60:20:20) | Pressure: 30 mTorr | ICP: 600 W | Bias: 30 W pulsed (1 kHz, 50% duty) | Temp: 80°C

| Parameter | Result |

|---|---|

| Si₃N₄ etch rate | 1.8 nm/s |

| SiO₂ etch rate | 0.032 nm/s |

| Selectivity (blanket) | 56:1 |

| Patterned selectivity (200 nm trenches) | 48:1 |

| SiO₂ sidewall deviation | < 5° |

| Polymer residue on oxide | < 2 nm |

Case Study 2: GaN over AlGaN for HEMT Gate Recess

Chemistry: Cl₂/BCl₃ (60:40) | Pressure: 5 mTorr | ICP: 800 W | Bias: 15 W DC (~18 eV) | Temp: 100°C

| Parameter | Result |

|---|---|

| GaN etch rate | 45 nm/min |

| AlGaN etch rate | 1.5 nm/min |

| Selectivity (blanket) | 30:1 |

| At very low bias (8 W, ~12 eV) | 50:1 (18 nm/min) |

| AlGaN surface roughness | Ra < 1 nm |

| Damage depth | ~2 nm (recoverable) |

Case Study 3: Selective SiGe Etch for GAA Transistor Release

Chemistry: CF₄/O₂/Ar (50:15:35) | Pressure: 40 mTorr | ICP: 500 W | Bias: 25 W pulsed (50 kHz, 30% duty) | Temp: 40°C

| Parameter | Result |

|---|---|

| SiGe etch rate | 0.5 nm/s |

| Si etch rate | 0.002 nm/s |

| Selectivity (blanket) | 250:1 |

| Patterned selectivity (10 periods) | 180:1 |

| Si nanosheet damage | < 0.5 nm by XPS |

| Repeatability (wafer-to-wafer) | < 12% variation |

Case Study 4: MEMS Release Etch — Selective Removal of Sacrificial Oxide

Chemistry: CF₄/O₂ (75:25) | Pressure: 20 mTorr | ICP: 400 W | Bias: 40 W | Temp: 25°C

| Parameter | Result |

|---|---|

| SiO₂ etch rate | 50 nm/min |

| Polysilicon etch rate | 2.5 nm/min |

| Selectivity | 20:1 |

| Stiction coefficient | < 0.01 (vs. 0.02–0.05 wet HF) |

| Resonator yield | 92% (vs. 88% wet HF) |

| Q-factor (cantilevers) | 50K–80K (vs. 40K–50K wet) |

Case Study 5: Photonic Waveguide Etch — Si over SiO₂ in SOI

Chemistry: Cl₂/HBr/O₂ (40:30:30) | Pressure: 5 mTorr | ICP: 700 W | Bias: 20 W | Temp: 20°C

| Parameter | Result |

|---|---|

| Si etch rate | 150 nm/min |

| SiO₂ etch rate | 0.8 nm/min |

| Selectivity | 188:1 |

| Sidewall roughness | Ra = 8–12 nm |

| Propagation loss (TE mode) | 3.2 dB/cm |

| Feature verticality | ±2° sidewall angle |

Current Limitations and Open Problems

The Fundamental Chemical Selectivity Limit

The ultimate limit of chemical selectivity arises when both the target material and the stop layer produce similarly volatile products in the plasma. For example, Si and SiO₂ in pure Cl₂ plasma both form volatile chloride products (SiCl₄). Selectivity relies on differences in reaction kinetics, not thermodynamics, and cannot exceed ~5–10:1 without invoking other mechanisms. When facing this limit, selective etch becomes ALE-based or requires passivation strategies.

Aspect-Ratio-Dependent Etch Rate (ARDE) Effects on Selectivity

High-aspect-ratio (HAR) structures exhibit different selectivity than blanket films or low-AR patterns due to ion scattering, local gas depletion, polymer redistribution, and charging effects.

Practical consequence: Selectivity measured on blanket films may be 50:1, but in HAR patterned structures (AR > 20), selectivity can degrade to 30:1 or lower. This 20–30% loss must be accounted for in process design.

Selectivity Degradation with Chamber Aging

Vacuum chambers naturally accumulate deposits on walls and electrodes, changing the chemistry and gas-phase composition over time. A process that achieves 50:1 selectivity with a freshly conditioned chamber may only achieve 40:1 after 100 wafers. This requires periodic chamber conditioning and real-time selectivity monitoring.

Gap Between Blanket-Film and Patterned-Structure Selectivity

Blanket film selectivity typically exceeds patterned selectivity by 10–30% due to microloading, shadowing effects, redeposition, and notching. A rule of thumb: patterned selectivity ≈ 80–90% of blanket selectivity.

Selectivity in Complex 3D Structures

The 3D NAND Channel Etch

Current production devices stack 200+ alternating SiO₂/Si₃N₄ layers, requiring a single etch step to penetrate through the entire stack — creating channel holes with aspect ratios exceeding 60:1 and depths beyond 8 μm. The selectivity challenge is multifaceted: mask selectivity (> 4:1 for amorphous carbon hardmask), layer-to-layer rate matching, and depth-dependent selectivity changes as the ion angular distribution narrows at extreme aspect ratios.

CFET: The Ultimate Selectivity Challenge

Looking ahead to complementary FET (CFET), which stacks an NMOS device directly on top of a PMOS device, the selectivity requirement for SiGe:Si jumps to > 500:1 in patterned structures. Current best-demonstrated patterned selectivity is ~200:1 (Case Study 3). CFET will require ALE-based SiGe removal, vapor-phase HCl etching, or novel combined selective deposition/etch approaches — representing the frontier of what plasma processing must achieve by the 2028–2030 timeframe.

Selectivity Troubleshooting Quick Reference

| Problem | Root Cause | Solution |

|---|---|---|

| Selectivity too low | Chemistry/energy not optimized for material pair | Reduce bias; add polymer-forming gas (C₄F₈, CHF₃); try pulsed plasma |

| Selectivity varies across wafer | Gas flow or temperature non-uniformity | Check gas showerhead; improve chuck temperature uniformity |

| Selectivity degrades over time | Chamber wall condition drift | Periodic O₂ plasma cleans; track selectivity per wafer; season chamber |

| Selectivity OK on blanket, poor on pattern | ARDE, microloading, or redeposition effects | Adjust pressure; tune gas chemistry for pattern loading |

| Selectivity collapses at high AR | Ion energy changes at feature bottom; gas depletion | Reduce pressure; increase gas flow; consider multi-step recipe |

| Polymer buildup killing selectivity | Over-passivation from fluorocarbon chemistry | Reduce polymer-forming gas flow; add O₂ flash between steps; increase temperature |

Emerging Technology Trends

EUV Lithography and the Selectivity Bottleneck

EUV enables 13–16 nm half-pitch patterning, but at these scales even 1–2 nm of unintended stop-layer etch becomes unacceptable. Thinner photoresists (< 30 nm) and pattern density variations exacerbate selectivity challenges. EUV adoption is driving demand for selectivities > 100:1 where 50:1 was previously acceptable.

Backside Power Delivery Networks (BPDNs)

Next-generation packaging requires selective etching of through-silicon vias (TSVs) and backside interconnects. Much higher aspect ratios (AR > 50:1) exacerbate ARDE effects, and thermal/mechanical constraints limit tuning options.

The Convergence of Etch and Deposition

Selective etching is being complemented by area-selective deposition (ASD) — the inverse of selective etch. The trend is toward process sequences combining selective etch and selective deposition for both the speed of selective etch and the low-damage advantages of selective deposition.

Atomic-Precision Processing: The Long-Term Vision

The convergence of ALE (selective removal), ALD (selective deposition), atomic layer cleaning (ALC), and atomic layer doping (ALDo) in integrated platforms represents the manufacturing paradigm for sub-1 nm node devices. For research labs, the ability to perform multiple atomic-layer processes on a single ICP-RIE platform provides a practical stepping stone toward this integrated vision.

Conclusion

Etch selectivity is no longer a “nice to have” — it is a make-or-break parameter for virtually every advanced plasma etch process. As layers get thinner, stacks get taller, and materials get more diverse, the demand for selectivity will only intensify. EUV lithography, GAA transistor architecture, 3D NAND stacking, and BPDN integration all push selectivity requirements beyond 100:1.

The good news is that multiple knobs are available to improve selectivity: gas chemistry, ion energy, pressure, temperature, pulsing, and ALE. The key is understanding which mechanism dominates your specific material system and optimizing accordingly.

NineScrolls’ ICP and RIE systems are built with the process flexibility needed for high-selectivity etch development. Independent power controls, wide pressure ranges, multi-gas configurations, comprehensive process monitoring, and optional cryogenic and ALE capabilities equip researchers to push the boundaries of selective plasma etching.

Related Articles in This Series

- Atomic Layer Etching for Semiconductor Manufacturing — detailed ALE processes for ultrathin films and precision requirements

- Cryogenic Plasma Etching vs. Bosch Process — comparing advanced silicon etch approaches

- Etching Beyond Silicon — plasma processing challenges for emerging semiconductor materials

- Machine Learning in Plasma Process Optimization — data-driven approaches to accelerating process development

Frequently Asked Questions

What is etch selectivity and why is it becoming more critical at advanced technology nodes?

Etch selectivity is the ratio of how fast you etch the target material versus the material you want to preserve. A selectivity of 50:1 means the target etches 50× faster than the stop layer. At advanced nodes (sub-7 nm), selectivity demands escalate dramatically because etch-stop layers thin from 10 nm to 2 nm — even small amounts of stop-layer consumption become unacceptable. Additionally, 3D architectures (GAA transistors, 3D NAND with 200+ layers) and self-aligned patterning processes all require selectivities well beyond 100:1. The general trend is approximately 2× selectivity increase per two technology generations.

What are the main mechanisms for achieving high selectivity in plasma etching?

Four primary mechanisms control etch selectivity: (1) Chemical selectivity — exploiting differences in etch product volatility (e.g., the target forms volatile fluorides while the stop layer forms involatile products); (2) Ion-energy-dependent selectivity — operating below the ion energy threshold of the stop material while above the threshold for the target (the basis of ALE selectivity); (3) Passivation-based selectivity — engineering a protective polymer layer on the stop material using fluorocarbon chemistry; (4) Temperature-dependent selectivity — exploiting different activation energies for surface reactions on different materials. The most effective processes often combine multiple mechanisms simultaneously.

Why does selectivity measured on blanket films differ from selectivity in patterned structures?

Blanket film selectivity typically exceeds patterned selectivity by 10–30% due to several pattern-dependent effects: (1) Microloading — features at different pitches experience different selectivity due to localized gas depletion; (2) ARDE — aspect-ratio-dependent etch rate changes alter the ion-to-radical ratio at feature bottoms; (3) Redeposition — sputtered products redeposit on stop materials in confined geometries; (4) Charging effects — aspect-ratio-dependent charging creates electric fields that alter ion trajectories. A practical rule of thumb is: patterned selectivity ≈ 80–90% of blanket selectivity. Always validate selectivity on relevant patterned test structures.

How does pulsed plasma improve etch selectivity?

Pulsed plasma (alternating between on and off states at 100 Hz to 10 kHz) improves selectivity through several mechanisms: during the plasma-off phase, reactive radicals continue chemical etching while ion bombardment stops, effectively separating the chemical and physical etch components. This allows the chemical selectivity to dominate. Additionally, during the off phase, residual radicals deposit protective polymer preferentially on the stop layer, enhancing passivation-based selectivity. Charged species also recombine during the off phase, reducing overall damage. Pulsed bias (while maintaining continuous ICP) and synchronous/asynchronous pulsing offer further tuning possibilities for specific material systems.

What ICP-RIE system features are most important for achieving high etch selectivity?

The most critical ICP-RIE system features for high selectivity are: (1) Independent source and bias power control — the ability to generate high radical densities (high ICP power) while maintaining very low ion energies (5–50 W bias) is essential; (2) Wide pressure range — high-selectivity processes typically operate at 10–50 mTorr, requiring stable plasma operation across a wide range; (3) Multi-gas capability — selectivity optimization often requires complex gas mixtures (fluorocarbon + hydrogen + oxygen + inert) with precise flow control; (4) Substrate temperature control — temperature tuning is a powerful selectivity lever, especially for cryogenic processes; (5) Pulsing capability — both ICP and bias pulsing with flexible frequency and duty cycle control; (6) In-situ monitoring — OES and ellipsometry for real-time selectivity tracking and endpoint detection.

References and Further Reading

- Oehrlein, G. S., et al. “Future of plasma etching for microelectronics: Challenges and opportunities.” J. Vac. Sci. Technol. B 42, 041501 (2024).

- Donnelly, V. M., & Kornblit, A. “Plasma etching: Yesterday, today, and tomorrow.” J. Vac. Sci. Technol. A 31, 050825 (2013).

- Huang, S., et al. “Plasma etching of high aspect ratio features in SiO₂ using Ar/C₄F₈/O₂ mixtures: A computational investigation.” J. Vac. Sci. Technol. A 37, 031304 (2019).

- Engelmann, S. U., et al. “Atomic-layer-etching (ALE): An emerging technique for etch selectivity and profile control.” J. Vac. Sci. Technol. A 40, 050404 (2022).

- Cooke, D. W., et al. “Silicon photonics waveguide etching and integration challenges.” IEEE J. Sel. Top. Quantum Electron. 24, 4700710 (2018).