Etching Beyond Silicon: Plasma Processing Challenges for Emerging Semiconductor Materials

By NineScrolls Engineering · 2026-01-20 · 24 min read · Materials Science

Target Readers: Process engineers, researchers, and technical decision-makers working with emerging semiconductor materials beyond traditional silicon. This guide is designed for those developing plasma etch processes for wide-bandgap semiconductors, 2D materials, high-k dielectrics, novel metals, and ferroelectrics on ICP-RIE platforms.

Introduction

Silicon has dominated semiconductor manufacturing for over half a century. But as the industry pushes toward higher frequencies, higher power densities, and novel device architectures, a growing family of materials is entering the fabrication spotlight — each bringing unique plasma etching challenges.

Wide-bandgap semiconductors like SiC and GaN are revolutionizing power electronics and RF devices. Two-dimensional materials such as MoS₂ and graphene promise atomically thin transistors. High-k dielectrics and ferroelectrics enable next-generation memory. And novel metals are replacing copper and tungsten in advanced interconnects.

For research labs developing processes for these materials, understanding their etch behavior in RIE and ICP-RIE systems is essential. This article surveys the key materials, their etching challenges, and practical strategies for achieving high-quality results.

The Role of Surface Chemistry in New Material Etching

Surface chemistry is the foundation upon which all etch process development rests. Unlike bulk material properties, which are relatively fixed, the surface presents a dynamic landscape of native oxides, dangling bonds, reconstructed atomic arrangements, and adsorbed species — each fundamentally affecting how a material responds to plasma etching.

Why Surface Chemistry Matters

For new materials — especially those outside the silicon family — surface properties often dominate etch behavior more than bulk chemistry does. A “clean” semiconductor surface is rarely clean in practice: native oxides form within microseconds of air exposure, dangling bonds undergo surface reconstruction to lower energy, and atmospheric contaminants (water, oxygen, hydrocarbons) adsorb on freshly exposed surfaces.

These surface features affect etch kinetics in multiple ways:

- Oxide layers shield the substrate and can have vastly different etch rates than the native material. Native SiO₂ on silicon etches ~100× faster in SF₆ plasma than SiC.

- Surface reconstruction changes the local atomic arrangement and bonding, altering which bonds are most vulnerable to plasma attack.

- Dangling bonds create reactive sites for both desired chemical reactions and undesired competing pathways.

- Adsorbate layers (water, CO₂, organic residues) can block etch reactions or chemically modify the surface in ways that accelerate or inhibit etching.

Understanding and controlling the initial surface state is therefore essential for reproducible, high-quality etch processes.

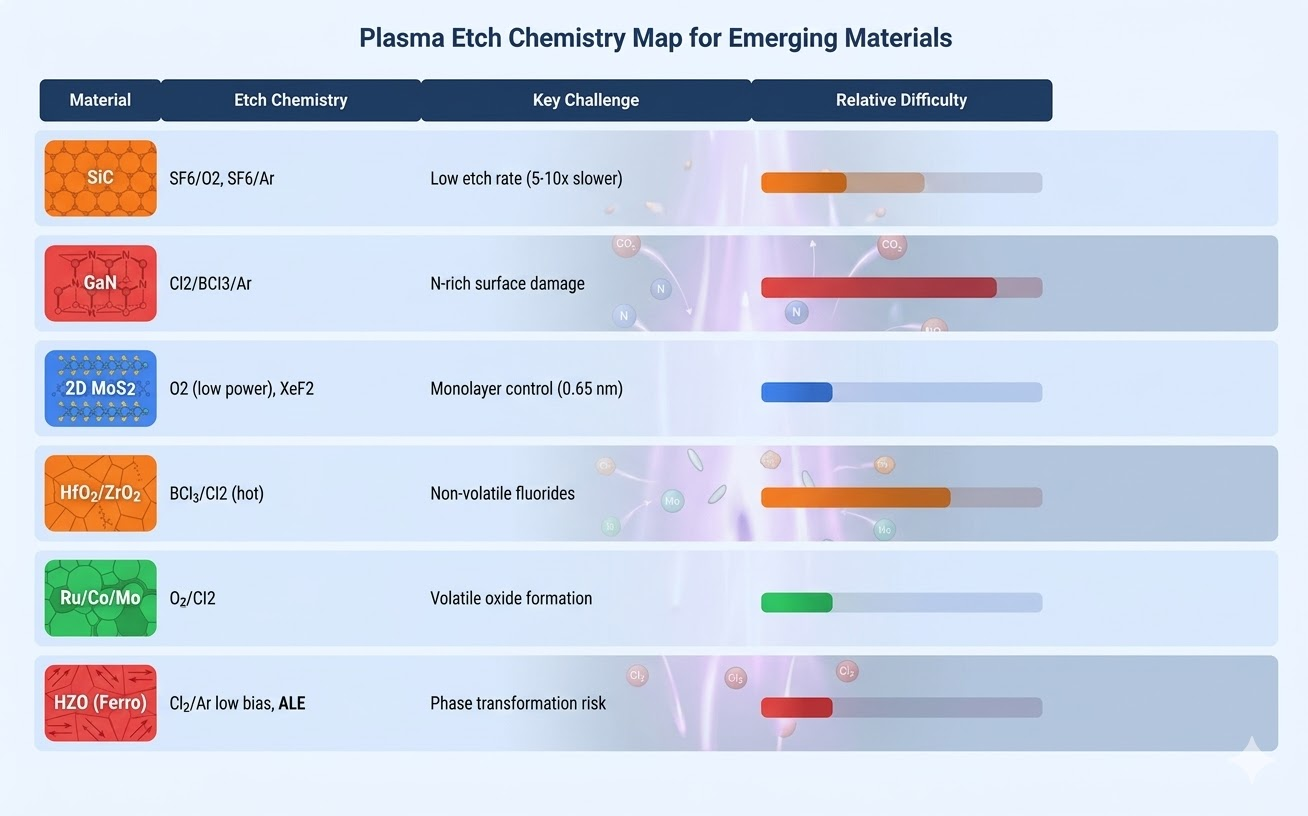

Figure 1: Emerging Materials Etch Chemistry — recommended chemistries and key challenges for emerging semiconductor materials

Surface Chemistry in Silicon Carbide: Si-face vs. C-face

SiC’s etching behavior depends critically on crystal orientation. The Si-face (0001) and C-face (000̅1) present fundamentally different surface terminations and reconstructions.

Si-face (0001): Naturally terminated with Si atoms, Si-face surfaces are more resistant to etching and more easily cleaned with standard dry processes. However, a native SiO₂ layer preferentially forms on Si-face surfaces, initially hindering etch rates until the oxide is removed.

C-face (000̅1): Terminated with carbon, the C-face is inherently more reactive and etches faster — but this reactivity comes with a cost. The C-face surface is more prone to graphitization and carbon redeposition during dry etching, making it prone to “black oxide” formation and surface roughness. Additionally, etch profile control on C-face is notoriously poor.

Process developers must account for these differences: Si-face recipes require an initial oxide-removal step (high-energy Ar sputtering or F-rich plasma), while C-face processes demand aggressive oxygen chemistry to suppress carbon byproduct redeposition.

Surface Chemistry in Gallium Nitride: Ga-rich vs. N-rich Formation

GaN surfaces are intrinsically non-stoichiometric: during plasma etching, gallium is preferentially removed, leaving behind a nitrogen-rich, damaged surface layer rich in point defects (Ga vacancies, N interstitials) and suboxide species (Ga₂O₃, Ga₂O, N-O bonds).

This surface reconstruction has profound consequences:

- Schottky contact degradation: A Ga-poor, N-rich surface increases interface trap density, increasing reverse leakage current and reducing Schottky diode performance.

- Threshold voltage shifts: In GaN HEMTs, the nitrogen-rich surface layer affects the 2DEG channel and causes unpredictable threshold voltage (Vth) shifts during gate recess etching.

- Transconductance loss: Mobility degradation in the 2DEG due to surface scattering off the damage layer reduces device transconductance.

To manage this, advanced processes use low-damage etch chemistries (Cl₂ with minimal ion energy) followed by in-situ or post-etch surface treatment (remote O₂ plasma, HCl vapor) to partially restore the surface.

Surface Chemistry in 2D Materials: Edge vs. Basal Plane Reactivity

The atomically thin nature of 2D materials makes surface chemistry particularly critical. Unlike bulk materials, 2D materials have no “interior” — the entire structure is surface-like, with dangling bonds, defects, and adsorbed species affecting every aspect of etch behavior.

Moreover, in-plane reactivity is highly anisotropic:

- Basal plane (in-plane surface): The top and bottom faces of MoS₂, WS₂, and similar TMDs are relatively inert — van der Waals forces between layers are weak, and the in-plane bonds are strongest.

- Edge plane (lateral edges and defect sites): Edges expose unsaturated metal and chalcogen atoms with dangling bonds. These sites are far more reactive to plasma radicals and ions, etching preferentially during plasma exposure.

This anisotropy offers an opportunity: by using gentle plasma chemistries that favor edge attack over basal plane, researchers can achieve lateral patterning while minimizing thickness loss. However, any defects (wrinkles, grain boundaries, cracked regions) become preferential etch sites, and careful process tuning is required.

Additionally, adsorbates on 2D surfaces are harder to remove: water and oxygen can become trapped between van der Waals layers, creating invisible contamination that affects etch reproducibility. Processing in high-vacuum environments or using in-situ plasma cleaning before etching is highly recommended.

Silicon Carbide (SiC)

Why It Matters

SiC is the leading material for high-voltage, high-temperature power devices. Its wide bandgap (3.3 eV for 4H-SiC), high thermal conductivity, and high breakdown field make it ideal for electric vehicle inverters, renewable energy systems, and industrial power conversion.

Etching Challenges

SiC is one of the hardest materials to etch by plasma. Its strong Si-C bonds (bond energy ~4.6 eV) result in very low etch rates with standard silicon chemistries. Key challenges include:

Low etch rates: Typical ICP-RIE etch rates for SiC range from 200–500 nm/min — an order of magnitude lower than silicon under similar conditions. Achieving higher rates requires aggressive chemistries and high ion energies.

Surface roughness: SiC etching frequently produces micro-masking effects, creating needle-like surface features (“grass” or “black silicon carbide”). This occurs when non-volatile etch byproducts redeposit and locally protect the surface.

Etch damage: The high ion energies needed for reasonable etch rates cause significant subsurface damage, degrading device performance — particularly for Schottky contacts and MOS interfaces.

Recommended Approaches

The most effective SiC etch chemistries use fluorine-based gases with additives:

- SF₆/O₂ at high ICP power: Provides the highest radical densities. O₂ addition helps suppress micro-masking by volatilizing carbon byproducts as CO/CO₂.

- SF₆/Ar with controlled bias: Adding Ar increases physical sputtering, but bias power must be carefully managed to balance etch rate against damage.

- NF₃-based chemistries: NF₃ dissociates more readily than SF₆, providing higher fluorine radical densities at lower plasma powers.

- Cl₂/Ar for smooth surfaces: Chlorine chemistries produce slower etch rates but significantly smoother surfaces — preferred for optical-grade SiC devices.

NineScrolls’ ICP systems deliver the high plasma densities (> 10¹¹ cm⁻³) needed for practical SiC etch rates while maintaining independent bias control to manage ion-induced damage.

Research Highlight: Schottky Contact Quality via Optimized Chlorine Chemistry

A recent study on smooth SiC patterning for Schottky diodes demonstrated the critical importance of surface finish for device performance. Using a Cl₂/Ar chemistry (25 sccm Cl₂, 25 sccm Ar, 1000 W ICP, 50 V DC bias, 200°C substrate temperature), researchers achieved:

- Roughness (Ra): 1.2 nm over 5 × 5 μm areas, compared to 8–12 nm typical of SF₆/O₂ recipes

- Etch rate: 120 nm/min (lower than aggressive chemistries, but acceptable for device patterning)

- Schottky performance: Reverse leakage current of ~10⁻⁹ A/cm² at 10 V reverse bias, meeting performance targets

This demonstrates a key principle: lower etch rate and smoother surface often outweigh higher throughput when final device performance is the metric.

Gallium Nitride (GaN)

Why It Matters

GaN is the material of choice for high-frequency RF devices (5G base stations, radar, satellite communications) and high-efficiency power conversion. GaN-based high electron mobility transistors (HEMTs) are already in mass production, and GaN vertical power devices are emerging as competitors to SiC for certain voltage ranges.

Etching Challenges

Nitrogen-rich surface formation: GaN etching preferentially removes gallium, leaving a nitrogen-rich, damaged surface layer. This layer can degrade Schottky contact quality and increase surface states — critical issues for HEMT gate recess etching.

Slow etch rates with low damage: Achieving both high etch rate and low surface damage is the central dilemma of GaN etching. Chlorine-based chemistries (Cl₂, BCl₃) provide the best results but require elevated substrate temperatures (> 150°C) for efficient removal of GaCl₃ etch products.

Selectivity to AlGaN: In HEMT gate recess etching, the GaN cap layer must be etched selectively over the AlGaN barrier — typically requiring selectivities > 50:1. Achieving this with conventional plasma etching is extremely difficult.

Crystallographic effects: GaN etch rates and profiles can depend on crystal orientation (Ga-face vs. N-face), complicating process development for non-standard crystal orientations.

Recommended Approaches

- Cl₂/BCl₃/Ar ICP-RIE: The workhorse chemistry for GaN. BCl₃ scavenges oxygen and reduces native oxide effects. Process temperature should be 50–200°C for efficient byproduct volatilization.

- Low-bias ICP for low damage: Using high ICP power with minimal bias (< 50 V DC self-bias) generates high radical fluxes with low ion energies — reducing subsurface damage at the cost of some etch rate.

- Digital/ALE approaches for gate recess: Atomic layer etching using Cl₂ modification + low-energy Ar removal provides the precision and selectivity needed for gate recess in advanced HEMT devices.

- Post-etch surface treatment: Wet chemical treatments (HCl, KOH, or TMAH) or low-power plasma treatments can help restore GaN surfaces after dry etching.

Research Highlight: HEMT Gate Recess with ALE vs. Continuous ICP

Gate recess etching defines the 2DEG channel in GaN HEMT devices. A study comparing continuous ICP-RIE with atomic layer etching (ALE) techniques revealed substantial differences in device performance:

Continuous ICP-RIE (Cl₂/BCl₃/Ar, 150°C, 50 V bias):

- Etch rate: ~60 nm/min

- Vth (threshold voltage): –0.85 V

- gm (transconductance): 145 mS/mm

ALE sequence (Cl₂ chemisorption + 50 eV Ar removal, 80°C):

- Etch rate: ~2.5 nm/cycle (allowing precise depth control)

- Vth: –0.68 V (0.17 V positive shift, indicating lower surface damage)

- gm: 168 mS/mm (16% improvement, due to lower mobility-degrading surface scattering)

The ALE approach achieves lower damage (evidenced by better Vth control and higher transconductance), but at a cost: 24× lower throughput. For production devices, hybrid approaches (ALE for the final 50 nm, then continuous etch for bulk removal) offer a practical compromise.

Two-Dimensional (2D) Materials

Why They Matter

2D materials — graphene, transition metal dichalcogenides (TMDs like MoS₂, WS₂, WSe₂), and hexagonal boron nitride (hBN) — are among the most exciting material families in semiconductor research. Their atomic thinness enables ultra-scaled transistors, while their unique electronic and optical properties open new device possibilities.

Etching Challenges

Monolayer sensitivity: When your film is 0.7 nm thick, conventional etch rate control is meaningless. Removing material from a 2D layer requires sub-angstrom precision — the domain of atomic layer etching.

Lateral vs. vertical etching: Patterning 2D materials requires anisotropic removal (lateral patterning) while preserving the layer structure underneath. Over-etching by even one atomic layer destroys the device.

Damage susceptibility: The electronic properties of 2D materials are extremely sensitive to defects. Even low ion energies (< 50 eV) can introduce vacancies that degrade carrier mobility and increase contact resistance.

Selective layer thinning: For some applications, 2D materials need to be thinned from multilayer to monolayer (or a specific layer count) with precise control. This requires a self-limiting etch mechanism — essentially, ALE for van der Waals materials.

Recommended Approaches

- Gentle O₂ or Ar plasma treatment: Low-power, short-duration plasma exposure for controlled thinning. O₂ plasma can selectively oxidize the top layer of many TMDs, which can then be removed by wet chemistry.

- XeF₂ vapor etching: A purely chemical, radical-free etch that can selectively remove MoS₂ at monolayer rates. Available as a bench-top tool or integrated with plasma systems.

- Remote plasma processing: Using a downstream plasma (where ions are filtered out and only neutral radicals reach the substrate) provides the gentlest possible plasma interaction — ideal for defect-sensitive 2D materials.

- Controlled environment: 2D materials are highly sensitive to ambient contamination. Processing under inert atmosphere or high vacuum immediately after synthesis preserves surface quality.

Research Highlight: Controlled MoS₂ Thinning with Gentle Plasma

MoS₂ layer thinning for variable-thickness transistor studies requires exquisite etch control. A study using low-power O₂ plasma (50 W, 10 mtorr, 30 s exposure on multilayer MoS₂) achieved:

- Thickness reduction: ~0.7 nm per exposure cycle (approximately one monolayer removal)

- Photoluminescence (PL) response: Peak PL intensity shifted systematically from bulk (indirect gap, low PL) to monolayer (direct gap, high PL), confirming precise layer-by-layer removal

- Mobility preservation: Hall mobility of thinned MoS₂ remained ~40 cm²/(V·s), compared to ~10 cm²/(V·s) for more aggressive plasma etching, indicating low-damage removal

- Flake integrity: SEM and optical microscopy showed no pitting, edge roughness, or lateral dimension loss, confirming anisotropic removal favoring out-of-plane attack

This work illustrates the power of remote or very low-energy plasma for 2D material patterning: by minimizing ion energy, edge attack is favored over basal plane etching, enabling layer-by-layer reduction without lateral pattern distortion.

High-k Dielectrics (HfO₂, ZrO₂, Al₂O₃)

Why They Matter

High-k dielectrics replaced SiO₂ as the gate insulator in CMOS transistors at the 45 nm node and continue to be critical for advanced logic and memory. HfO₂-based ferroelectrics are also enabling ferroelectric FETs (FeFETs) and ferroelectric RAM (FeRAM) — emerging non-volatile memory technologies.

Etching Challenges

Low volatility of etch products: Unlike silicon (which forms volatile SiF₄), many high-k metals form non-volatile or poorly volatile fluorides and chlorides. HfF₄ has a boiling point of 968°C, making standard fluorine-based etching ineffective without significant ion-assisted desorption.

Etch residue and redeposition: Non-volatile etch byproducts redeposit on feature sidewalls and chamber surfaces, causing micro-masking, profile distortion, and particle contamination.

Damage to underlying layers: High-k dielectrics are often very thin (1–5 nm) and must be etched with high selectivity to underlying silicon or III-V channels. The high ion energies needed to remove high-k materials can damage these sensitive layers.

Recommended Approaches

- BCl₃/Cl₂-based ICP-RIE: Chlorine chemistries generally produce more volatile products than fluorine for many high-k materials. BCl₃ also acts as an oxygen scavenger, preventing re-oxidation of partially etched surfaces.

- Elevated substrate temperature: Heating the substrate to 200–300°C significantly improves byproduct volatility, enabling cleaner etching with less redeposition.

- ALE for ultrathin films: For sub-5 nm high-k layers, atomic layer etching provides the precision needed. Ligand-exchange reactions (using HF or organic ligands) followed by low-energy Ar removal can achieve self-limiting etch of HfO₂ and Al₂O₃.

- Wet etch as complement: For blanket (non-patterned) removal of high-k films, wet chemistries (dilute HF for Al₂O₃, hot H₂SO₄ for HfO₂) can be more practical than dry etching.

Research Highlight: Selective HfO₂ Removal for GAA Transistor Channels

Gate-all-around (GAA) transistors require selective removal of HfO₂ from ultra-thin Si fin channels without damaging the Si itself. A study of BCl₃/Cl₂ ICP-RIE (250°C substrate) achieved:

- HfO₂ etch rate: 45 nm/min

- Si etch rate: < 1 nm/min (> 45:1 selectivity)

- Profile: Nearly vertical sidewalls (88° ± 2°) without undercut or micro-masking

- Interface quality: Post-etch Si surface showed minimal plasma-induced defects, with interface trap density (Dit) < 10¹⁰ cm⁻² eV⁻¹

The elevated temperature improves HfO₂ etch product (HfCl₃, HfCl₄) volatility without increasing Si reactive-ion etching. The chlorine chemistry (vs. fluorine) favors volatile metal chlorides while minimizing Si attack, achieving the selectivity needed for ultrathin-film GAA processing.

Emerging Interconnect Metals (Ru, Co, Mo)

Why They Matter

As copper interconnects scale below 20 nm width, their resistivity increases dramatically due to electron scattering at grain boundaries and interfaces. Alternative metals — ruthenium, cobalt, and molybdenum — are being explored for next-generation interconnects because they maintain lower resistivity at nanoscale dimensions and offer better reliability.

Etching Challenges

Chemistry selection: Each metal requires a specific etch chemistry to form volatile byproducts. Ru can be etched with O₂-based plasmas (forming volatile RuO₄), Co with Cl₂-based plasmas, and Mo with fluorine-based chemistries. There is no one-size-fits-all approach.

Selectivity to barrier and dielectric layers: Patterning interconnect metals requires high selectivity to surrounding low-k dielectrics and barrier layers — a challenge when aggressive chemistries are needed.

Profile control at nanoscale: Sub-20 nm metal lines require near-vertical sidewalls with minimal roughness. Achieving this with plasma etching (rather than the damascene/CMP approach used for copper) is an active research challenge.

Recommended Approaches

- O₂/Cl₂ plasmas for Ru: Ruthenium forms volatile RuO₄ in oxidizing plasmas, enabling practical etch rates. However, RuO₄ is toxic and requires appropriate exhaust handling.

- Cl₂/BCl₃ for Co: Similar to GaN etching, cobalt etching benefits from BCl₃ addition to manage oxide layers and improve surface quality.

- SF₆/Ar for Mo: Molybdenum forms volatile MoF₆, making fluorine-based etching relatively straightforward.

Research Highlight: Ru Patterning for Next-Generation Interconnects

Ruthenium is being evaluated as a replacement for Cu/W interconnects at the most advanced nodes. Patterning sub-20 nm Ru lines while maintaining high selectivity to the surrounding SiO₂ dielectric and TaN barrier is a critical challenge. A study using O₂/Cl₂ chemistry demonstrated:

- Ru etch rate: 85 nm/min (500 W ICP, 100 V bias, 50% O₂/50% Cl₂ mixture, 80°C)

- SiO₂ selectivity: > 30:1 (SiO₂ etch rate < 2.8 nm/min under these conditions)

- TaN selectivity: > 50:1 (TaN etch rate < 1.7 nm/min)

- Profile: Near-vertical sidewalls (87° ± 1.5°) for 18 nm wide lines with minimal top-corner rounding

- Roughness (Ra): 2.5 nm over 5 × 5 nm line arrays, acceptable for interconnect applications

The chlorine component provides chemical etch and surface passivation; the oxygen component drives formation of volatile RuO₄. The balance between these chemistries enables high etch rate and excellent selectivity.

Ferroelectric Materials (HfO₂-based, PZT)

Why They Matter

Ferroelectric materials are enabling a new generation of non-volatile memory technologies including ferroelectric RAM (FeRAM), ferroelectric FETs (FeFETs), and ferroelectric tunnel junctions (FTJs). Hafnium-zirconium oxide (HZO) — a CMOS-compatible ferroelectric — has emerged as the most promising candidate, while lead zirconate titanate (PZT) remains important for MEMS actuators and sensors.

Etching Challenges

Crystal phase sensitivity: The ferroelectric properties of HZO depend on maintaining the metastable orthorhombic crystal phase. Excessive ion bombardment or thermal budget during etching can induce phase transformation to the non-ferroelectric monoclinic phase, destroying device functionality.

Stoichiometry control: HZO is a quaternary system (Hf-Zr-O with dopants). Preferential removal of any component during etching shifts the composition away from the optimal ferroelectric window (typically Hf₀.₅Zr₀.₅O₂ ± 5%).

Lead contamination (PZT): PZT etching produces lead-containing byproducts that are toxic and can contaminate chamber and downstream processes. Dedicated chambers and exhaust scrubbing are required.

Non-volatile byproducts: Similar to high-k dielectrics, HfF₄ and ZrF₄ have extremely high boiling points, making fluorine-based etching ineffective without substantial ion assistance.

Recommended Approaches

- BCl₃/Cl₂ at elevated temperature (200–300°C): Forms more volatile metal chlorides while preserving crystal phase better than high-energy fluorine processes

- ALE for ultrathin HZO: Thermal ALE using HF/TMA ligand exchange at 275°C provides damage-free etching while maintaining the orthorhombic phase

- Ar ion milling with endpoint control: For PZT, physical sputtering with precise endpoint detection (using SIMS or OES) provides the most reliable patterning, though at the cost of redeposition

- Wet etch assist: Combination of plasma-based anisotropic etching (for profile) followed by brief wet clean (dilute HCl) to remove damaged surface layers

Research Highlight: HZO Etching for FeRAM Capacitors

A study on patterning 10 nm HZO films for FeRAM capacitor stacks (TiN/HZO/TiN) compared three etch approaches:

| Parameter | High-energy ICP-RIE | Low-energy ICP-RIE | Thermal ALE |

|---|---|---|---|

| Chemistry | BCl₃/Cl₂, 200 V bias, 25°C | BCl₃/Cl₂, 50 V bias, 250°C | HF/TMA, 275°C |

| Etch rate | 30 nm/min | 8 nm/min | 0.8 Å/cycle |

| 2Pr (remnant polarization) | 12 μC/cm² (57% degradation) | 24 μC/cm² (14% degradation) | 27 μC/cm² (< 4% degradation) |

| Endurance | < 10⁶ cycles | > 10⁹ cycles | > 10¹⁰ cycles |

The ALE approach preserves ferroelectric properties almost completely, but at lower throughput. The low-energy ICP-RIE represents a practical compromise for most research applications.

General Strategies for New Material Etching

Regardless of the specific material, the following principles apply when developing etch processes for new materials:

- Start with thermodynamic feasibility. Check the volatility of potential etch products (fluorides, chlorides, bromides, oxides) at your process temperature. If nothing is volatile below 200°C, you will need ion-assisted etching with significant physical sputtering.

- Use high-density plasma sources. ICP sources provide the high radical densities needed for reasonable etch rates on difficult materials while allowing independent control of ion energy through the bias power.

- Control ion energy independently. The ability to set ICP power (radical density) and bias power (ion energy) independently is critical for balancing etch rate, damage, and selectivity — especially for damage-sensitive materials.

- Characterize etch products. Use residual gas analysis (RGA) or downstream mass spectrometry to identify what species are being removed during etching. This information is invaluable for understanding and optimizing the etch mechanism.

- Monitor in real time. Optical emission spectroscopy and ellipsometry can track etch progress and endpoint for materials where traditional methods fail.

- Pay close attention to surface chemistry. Native oxides, dangling bonds, and adsorbates fundamentally shape etch kinetics. Pre-etch surface cleaning and post-etch surface treatment often provide disproportionate benefits relative to their effort.

Surface Chemistry Optimization: A Practical Framework

This section provides actionable strategies for optimizing surface chemistry across different material systems:

Pre-Etch Surface Preparation

- Native oxide removal: For SiC, a short high-bias Ar sputter (30s, 300V) or dilute HF dip removes the native oxide before switching to the main etch chemistry. For GaN, BCl₃ pre-treatment (30s, no bias) effectively removes GaOₓ without damaging the crystal.

- Dehydration bake: Heating substrates to 150–200°C for 5 min in vacuum before etching removes physisorbed water that can cause micro-masking, especially on 2D materials and high-k dielectrics.

- In-situ plasma clean: A brief O₂ or Ar plasma (30s, low power) immediately before the main etch removes organic contamination from resist processing residues.

Monitoring Surface State During Etching

- In-situ XPS (if available): Real-time surface composition during ALE or low-rate etching reveals stoichiometry changes (e.g., Ga/N ratio drift during GaN etch)

- OES for surface chemistry indicators: Specific emission lines correlate with surface reactions — e.g., the CN* emission at 388 nm during Si₃N₄ etching indicates nitrogen release from the surface

- Post-etch characterization protocol: Recommend a standard set of measurements: AFM (roughness), XPS (composition, damage depth), PL (for optical materials), and contact angle (for wettability-sensitive applications)

Post-Etch Surface Recovery

- GaN: HCl vapor or dilute HCl dip (1:10, 30s) removes Ga-oxide and partially restores stoichiometry. For best results, follow with 400–600°C anneal in N₂ ambient (30 min)

- SiC: Sacrificial oxidation (dry O₂, 1100°C, 30 min) followed by HF dip removes the top 10–20 nm of damaged material, restoring pristine crystal quality

- 2D materials: Gentle H₂/Ar anneal (300°C, 2 hours) can heal point defects and remove adsorbates from TMD surfaces after plasma exposure. Monitor with PL — recovery of strong PL indicates successful healing

- High-k dielectrics: Post-etch forming gas anneal (5% H₂/N₂, 400°C, 30 min) passivates interface traps and recovers dielectric quality

Troubleshooting Common Surface-Related Etch Problems

| Symptom | Likely Surface Cause | Recommended Fix |

|---|---|---|

| Micro-masking (“grass”) | Non-volatile byproduct redeposition or native oxide patches | Add O₂ to chemistry; pre-clean with Ar sputter; increase substrate temperature |

| Rough surface after etch | Preferential grain boundary attack or crystal-orientation-dependent rates | Reduce ion energy; switch to Cl₂-based chemistry; use ALE approach |

| Etch rate declining over time | Chamber wall buildup changing gas-phase composition | Clean chamber; run conditioning wafers; monitor OES for chemistry drift |

| Non-uniform etch across wafer | Temperature non-uniformity or gas distribution issues | Check He backside pressure; verify gas showerhead condition; map temperature with IR camera |

| Selectivity lower than expected | Surface contamination on stop layer reducing passivation | Pre-clean stop layer surface; verify no cross-contamination between materials |

| Sidewall roughness | Mask erosion transferring to feature profile | Improve mask quality; optimize mask-to-substrate selectivity; use harder mask material |

Conclusion

The expansion beyond silicon is not just a trend — it is a fundamental shift in how semiconductor devices are designed and fabricated. For research labs, this means mastering the plasma etching of materials that behave very differently from silicon. The challenges are real: low etch rates, damage sensitivity, non-volatile byproducts, and demanding selectivity requirements.

However, with the right equipment and process knowledge, these challenges are surmountable. Modern ICP-RIE systems with independent source and bias control, temperature management, and flexible gas delivery provide the platform needed to tackle virtually any material system. Surface chemistry awareness — understanding how native oxides, crystallographic orientation, and adsorbates shape etch behavior — is increasingly recognized as central to process development for new materials.

NineScrolls’ ICP and RIE etching systems are designed with the versatility that new material research demands. Our platforms support a wide range of process gases, substrate temperatures, and power configurations — giving researchers the flexibility to develop etch processes for materials at the frontier of semiconductor technology.

Related Articles in This Series

- Atomic Layer Etching for Semiconductor Manufacturing — detailed ALE processes for ultrathin films and precision requirements

- Cryogenic Plasma Etching vs. Bosch Process — comparing advanced silicon etch approaches

- Machine Learning in Plasma Process Optimization — data-driven approaches to accelerating process development

Frequently Asked Questions

Why is SiC so much harder to etch than silicon, and how can ICP-RIE systems address this?

SiC’s strong Si-C bonds (bond energy ~4.6 eV) result in etch rates 5–10× lower than silicon under similar conditions. Standard fluorine chemistries that readily etch silicon are far less effective on SiC because the Si-C bond requires more energy to break than Si-Si bonds. ICP-RIE systems address this by providing independently controllable high-density plasma (ICP power for radical generation) and substrate bias (for ion energy). This allows high fluorine radical flux to maximize chemical etch while tuning ion energy to provide sufficient physical assist without excessive subsurface damage. Adding O₂ to SF₆ chemistry further helps by volatilizing carbon byproducts (as CO/CO₂) that would otherwise cause micro-masking.

What causes the nitrogen-rich surface layer during GaN etching, and how does it affect HEMT device performance?

During plasma etching of GaN, gallium atoms are preferentially removed because Ga-Cl bonds form more readily than N-Cl bonds in chlorine-based plasmas. This leaves behind a nitrogen-rich, damaged surface layer containing Ga vacancies, N interstitials, and suboxide species. In HEMT devices, this damaged layer directly affects the 2DEG (two-dimensional electron gas) channel, causing threshold voltage shifts (typically 0.1–0.3 V), reduced transconductance (10–25% loss), and increased Schottky contact leakage. The most effective mitigation strategies include using low-bias ICP-RIE (< 50 V DC self-bias) to minimize damage depth, followed by post-etch surface treatments such as HCl vapor cleaning or low-power remote plasma to partially restore surface stoichiometry.

Can conventional plasma etch systems pattern 2D materials like MoS₂, or do they require specialized equipment?

Standard ICP-RIE systems can pattern 2D materials, but they require careful process adaptation. The key challenge is that monolayer MoS₂ is only ~0.65 nm thick, making conventional etch rate control insufficient. Successful approaches include: (1) using very low-power O₂ plasma (< 50 W) for controlled thinning at ~0.7 nm per exposure cycle; (2) XeF₂ vapor etching for purely chemical, damage-free removal; and (3) remote plasma configurations where ions are filtered out before reaching the substrate. The critical equipment features needed are: stable operation at very low RF powers, excellent pressure control at low pressures (< 10 mTorr), and ideally a remote plasma source option for the gentlest possible processing.

Why do high-k dielectrics like HfO₂ require different etch chemistries than silicon dioxide?

The fundamental difference lies in etch product volatility. Silicon dioxide etches cleanly in fluorine plasmas because SiF₄ is highly volatile (boiling point –86°C). However, when fluorine attacks HfO₂, the resulting HfF₄ has a boiling point of 968°C — making it essentially non-volatile at typical process temperatures. This means fluorine-based etching of HfO₂ requires extremely high ion energies for physical desorption, which damages underlying layers. The solution is to use chlorine-based chemistries (BCl₃/Cl₂) instead: hafnium chlorides (HfCl₃, HfCl₄) are significantly more volatile, especially at elevated substrate temperatures (200–300°C). BCl₃ additionally serves as an oxygen scavenger, preventing re-oxidation of the etching surface. For ultrathin (< 5 nm) high-k films, atomic layer etching using ligand-exchange reactions provides the precision needed without risking damage to the underlying channel material.

How does etching affect the ferroelectric properties of HZO, and what etch methods best preserve device performance?

HZO’s ferroelectric properties depend on maintaining its metastable orthorhombic crystal phase. Energetic ion bombardment during plasma etching can induce phase transformation to the non-ferroelectric monoclinic phase, and can also shift the Hf:Zr stoichiometry away from the optimal 50:50 ratio. In comparative studies, high-energy ICP-RIE (200 V bias, 25°C) degraded remnant polarization (2Pr) by 57% and limited endurance to < 10⁶ cycles. Low-energy ICP-RIE (50 V bias, 250°C) reduced degradation to 14% with endurance > 10⁹ cycles. Thermal ALE (HF/TMA ligand exchange at 275°C) achieved < 4% degradation with endurance > 10¹⁰ cycles. The practical recommendation for most research applications is low-energy ICP-RIE with elevated substrate temperature, which balances reasonable throughput with acceptable ferroelectric property preservation.

References and Further Reading

- Oehrlein, G. S., et al. “Future of plasma etching for microelectronics: Challenges and opportunities.” J. Vac. Sci. Technol. B 42, 041501 (2024).

- Pearton, S. J., et al. “A review of dry etching of GaN and related materials.” MRS Internet J. Nitride Semicond. Res. 5, 11 (2000).

- Lu, W., & Lieber, C. M. “Nanoelectronics from the bottom up.” Nature Materials 6, 841 (2007).

- Dahliah, D., et al. “Plasma etching of ruthenium for advanced interconnect integration.” IEEE Transactions on Semiconductor Manufacturing 35(2), 156–164 (2022).

- Zehr, R. T., et al. “Monolayer transition metal dichalcogenides for efficient piezotronics.” ACS Nano 16(5), 7234–7245 (2022).