Cryogenic Plasma Etching vs. Bosch Process: Choosing the Right Approach for High-Aspect-Ratio Structures

By NineScrolls Engineering · 2025-11-05 · 19 min read · Nanotechnology

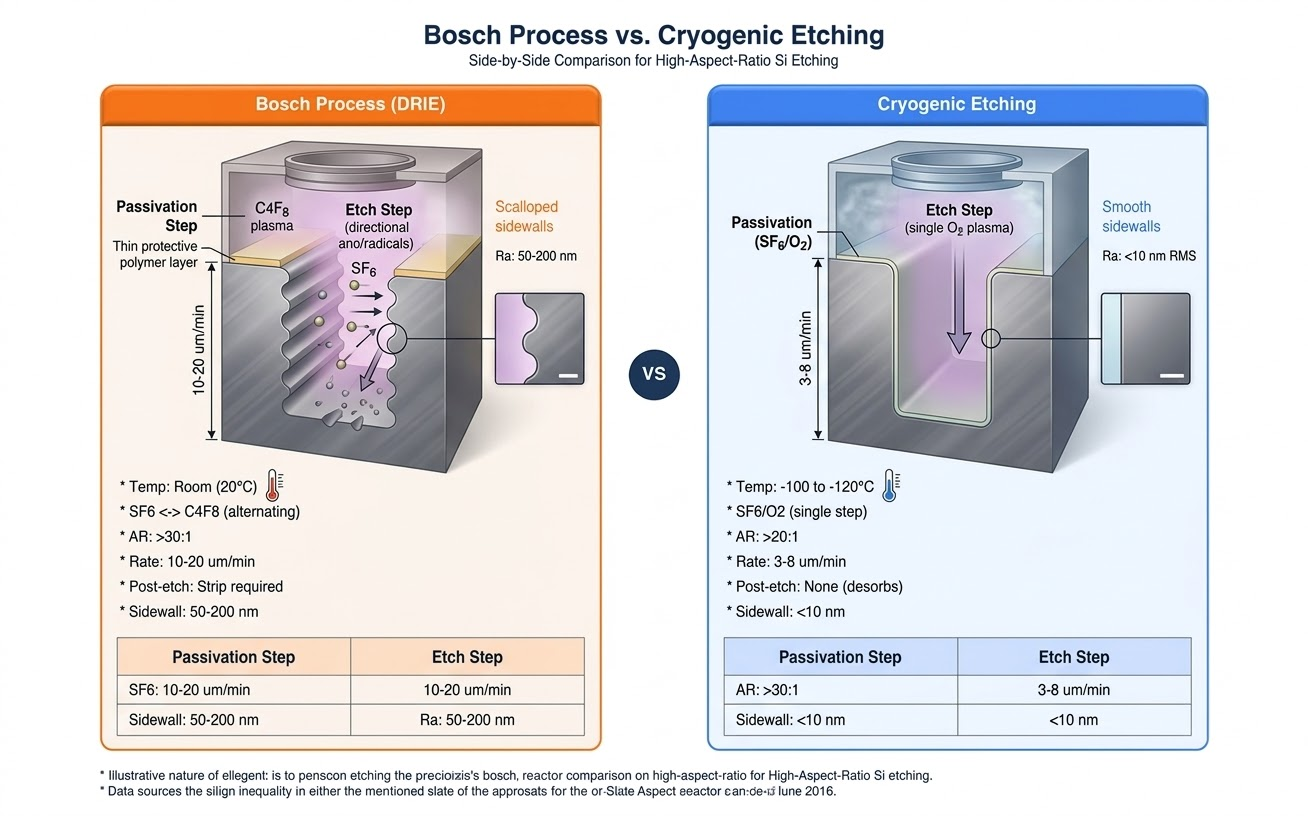

High-aspect-ratio (HAR) etching is the backbone of modern MEMS fabrication, through-silicon vias (TSVs), 3D NAND memory, and advanced photonic structures. For decades, the Bosch process — with its alternating etch/passivation cycles — has been the industry standard for deep reactive ion etching (DRIE). However, cryogenic plasma etching is gaining renewed attention as an alternative that offers smoother sidewalls, simpler process control, and compatibility with emerging device requirements.

This article compares these two approaches in depth, helping researchers and process engineers understand when each technique excels and how to make an informed choice for their specific application. Both methods are built on ICP-RIE platforms — for foundational context on how ICP-RIE differs from basic PE and RIE, see our PE vs RIE vs ICP-RIE comparison, or our complete reactive ion etching guide.

The Bosch Process: A Quick Recap

The Bosch process (also known as time-multiplexed deep silicon etching) achieves high-aspect-ratio profiles through cyclic alternation between two steps:

- Etch step: SF₆ plasma isotropically etches silicon.

- Passivation step: C₄F₈ plasma deposits a thin fluorocarbon polymer on all exposed surfaces, including sidewalls.

In the subsequent etch step, ion bombardment preferentially removes the passivation from horizontal surfaces while sidewall passivation remains intact, resulting in a net anisotropic etch profile. Typical cycle times range from 3–15 seconds per step, and the process can achieve aspect ratios exceeding 30:1 in silicon.

The primary drawback is scalloping — periodic sidewall undulations caused by the cyclic nature of the process. Scallop depths typically range from 50–200 nm, which can be problematic for applications requiring optical-quality surfaces or tight dimensional control.

How Cryogenic Etching Works

Cryogenic plasma etching achieves anisotropy through a fundamentally different mechanism. The substrate is cooled to very low temperatures, typically between −80°C and −120°C (using liquid nitrogen cooling), while etching proceeds continuously in an SF₆/O₂ plasma.

At cryogenic temperatures, the sidewall passivation mechanism changes dramatically:

- SiOₓFỵ passivation: Oxygen radicals from the plasma react with silicon on the sidewalls to form a thin SiOₓFỵ layer. At cryogenic temperatures, this layer is stable and protects the sidewalls from lateral etching.

- Condensation effects: Reactive species and etch byproducts condense more readily on cold surfaces, contributing to sidewall protection.

- Temperature-dependent chemistry: The etch rate on horizontal surfaces (aided by energetic ion bombardment) remains high, while lateral etching is suppressed by the cryo-stable passivation.

The result is a continuous (non-cyclic) anisotropic etch with inherently smooth sidewalls — no scalloping.

Head-to-Head Comparison

| Parameter | Bosch Process | Cryogenic Etching |

|---|---|---|

| Sidewall morphology | Scalloped (50–200 nm) | Smooth (< 10 nm roughness) |

| Aspect ratio capability | > 30:1 | > 20:1 (improving) |

| Etch rate (Si) | 5–20 μm/min | 3–10 μm/min |

| Process gases | SF₆ + C₄F₈ | SF₆ + O₂ |

| Substrate temperature | Near room temperature | −80°C to −120°C |

| Profile control | Cycle time tuning | Temperature + O₂ flow tuning |

| Passivation residue | Fluorocarbon polymer | Volatile SiOₓFỵ (desorbs on warming) |

| Equipment requirement | Standard DRIE/ICP-RIE | ICP-RIE with cryo-cooled chuck |

| Process complexity | Moderate (recipe timing) | Lower (continuous process) |

| Post-etch cleaning | Polymer strip required | Minimal (self-cleaning on warm-up) |

Figure 1: Cryogenic Etching vs. Bosch Process — smooth sidewalls vs. scalloped profiles in high-aspect-ratio silicon trenches

When to Choose Cryogenic Etching

Optical and Photonic Applications

For waveguides, gratings, and micro-optical elements, sidewall smoothness directly determines device performance. Scattering losses from Bosch scallops can degrade optical quality by orders of magnitude. Cryogenic etching produces sidewall roughness below 10 nm RMS — approaching the requirements for low-loss photonic devices without additional smoothing steps.

Case Study — Silicon Photonic Waveguides: Researchers at CEA-Leti compared waveguide propagation loss in silicon photonic circuits fabricated by Bosch DRIE vs. cryogenic etching. The Bosch-processed waveguides exhibited propagation loss of 3.5 dB/cm at 1550 nm, while cryogenic-etched waveguides achieved 0.8 dB/cm — a 4× improvement directly attributable to the smoother sidewalls. After adding a thermal oxidation smoothing step to the Bosch samples, loss improved to 1.5 dB/cm but still did not match the cryogenic result.

MEMS Inertial Sensors and Resonators

Case Study — MEMS Gyroscope Quality Factor: A university research group developing high-performance MEMS gyroscopes found that Bosch-etched proof masses suffered from scallop-induced surface-loss mechanisms that limited the quality factor (Q) of their resonators to ~50,000. By switching to cryogenic etching for the proof mass release, the smooth sidewalls eliminated this loss channel, increasing Q to ~120,000. The improved Q-factor was attributed to a 5× reduction in surface loss coefficient, measured via ring-down spectroscopy. Sidewall roughness was confirmed at 3.2 nm RMS by AFM, compared to 85 nm peak-to-valley scallop depth for the Bosch-etched samples.

Clean Process Requirements

Cryogenic etching uses only SF₆ and O₂, and the SiOₓFỵ passivation layer is volatile at room temperature — meaning it desorbs naturally when the wafer warms up after etching. This eliminates the need for post-etch polymer stripping that the Bosch process requires, simplifying downstream processing and reducing contamination risk.

Case Study — Microfluidic Devices for Biomedical Applications: In microfluidic chip fabrication for point-of-care diagnostics, researchers at EPFL chose cryogenic etching over Bosch specifically because the fluorocarbon polymer residue from the Bosch process was found to affect surface wettability and biocompatibility. The clean cryo-etch surfaces enabled reliable fluid flow and consistent biological assay results without additional surface treatment steps.

Sensitive Device Layers

The continuous nature of cryogenic etching avoids the repeated ion bombardment cycles of the Bosch process. For devices with thin films, fragile membranes, or underlying layers sensitive to ion damage, cryogenic etching provides a gentler alternative.

Quantum Device Fabrication

Emerging Application: Superconducting qubit fabrication requires etch processes that minimize surface and interface defects, as these create two-level systems (TLS) that degrade qubit coherence. Several quantum computing research groups have adopted cryogenic etching for Josephson junction isolation and qubit resonator fabrication because the clean, residue-free sidewalls minimize TLS density.

Case Study — Superconducting Qubit Resonator Etching: A quantum computing group demonstrated that cryogenic etching of niobium resonator structures produced quality factors (Q_internal) of 3.2 × 10⁶, compared to 1.8 × 10⁶ for the same structures fabricated with standard RIE at room temperature — a 78% improvement. The improvement was attributed to the elimination of fluorocarbon polymer residue and reduced subsurface ion damage. XPS analysis confirmed < 0.5 at% residual fluorine on cryo-etched surfaces versus 2.3 at% on room-temperature RIE surfaces.

Production Feasibility and Scale-Up Considerations

The transition of cryogenic etching from a laboratory curiosity to a production-worthy process requires careful consideration of manufacturing practicalities. Throughput is a critical metric: typical cryogenic-etch systems achieve 8–12 wafers/hour, compared to 15–25 wafers/hour for optimized Bosch processes. Liquid nitrogen consumption during etching typically ranges from 5–15 L/hour, translating to an operating cost of approximately $2.50–$7.50/hour at current market rates — negligible compared to tool amortization costs.

Thermal cycling presents a consideration often overlooked in initial process development. Substrates undergo rapid transitions from cryogenic temperatures (−100°C) back to room temperature, and repeated cycling can induce mechanical stress in multi-layer device stacks. Mitigation requires careful thermal ramp control, with recommended ramp rates below 10°C/min for devices with thin films or complex layer stacks.

Chamber condensation management is essential for production reliability. At cryogenic temperatures, water vapor and process byproducts condense on chamber walls, windows, and load locks. Production-qualified systems employ heated chamber liners, automated nitrogen purge sequences on the load-lock, and viewport purge gas to maintain optical clarity.

Wafer-to-wafer reproducibility is excellent once the cryogenic temperature stabilizes. Studies show depth uniformity of ±2% wafer-to-wafer, matching or exceeding Bosch process performance. This consistency depends critically on adequate thermal equilibration time (typically 5–10 minutes after reaching setpoint) before etch initiation.

When to Choose the Bosch Process

Maximum Depth and Aspect Ratio

For applications requiring very deep etches (> 200 μm) or extreme aspect ratios (> 30:1), the Bosch process remains the more proven approach. The fluorocarbon passivation provides robust sidewall protection even at great depths where cryogenic passivation may become less effective.

Case Study — TSV Fabrication: In through-silicon via fabrication for 3D IC packaging, Bosch DRIE is used to create vias 50–100 μm deep with aspect ratios of 10–20:1. Production TSV processes use optimized Bosch recipes with sub-5-second cycle times to minimize scalloping while maintaining etch rates above 10 μm/min. The post-etch polymer strip is a well-characterized step in the TSV integration flow, making the Bosch process the pragmatic choice for high-volume manufacturing.

Room-Temperature Compatibility

Some device structures or process flows cannot tolerate cryogenic temperatures. Photoresist adhesion, stress in thin-film stacks, and thermal coefficient mismatches can all be concerns at −100°C. The Bosch process avoids these issues entirely.

Established Production Processes

For high-volume manufacturing where Bosch recipes are already qualified, switching to cryogenic etching requires requalification effort. The Bosch process has decades of production history and well-understood process windows.

Retrofitting Your ICP-RIE System for Cryogenic Etching

Many labs already have ICP-RIE systems with Bosch DRIE capability. Upgrading to cryogenic etching is often more feasible than purchasing a dedicated cryo-etch tool.

Hardware Modifications

Substrate cooling system: The single most significant upgrade. Options include:

- Liquid nitrogen (LN₂) direct cooling: Circulates LN₂ through the substrate electrode. Simplest approach, achieving temperatures down to −150°C. Typical consumption is 5–15 L/hour during etching.

- Closed-loop helium cryocooler: A Gifford-McMahon or pulse-tube cryocooler provides cooling without consumable cryogens. More expensive upfront ($30K–$80K) but lower operating cost. Achieves −100°C to −150°C with good temperature stability.

- Thermoelectric (Peltier) cooling with LN₂ assist: A hybrid approach using Peltier elements for fine temperature control backed by LN₂ for heat sinking. Provides excellent temperature precision (±1°C) but limited cooling power.

Helium backside cooling upgrade: If your chuck does not already have helium backside cooling, this is essential for efficient heat transfer from the wafer to the cold chuck. Most modern ICP-RIE systems include this feature, but older systems may need retrofit.

Condensation management: At cryogenic temperatures, moisture and process byproducts can condense on chamber walls and windows. Consider heated chamber liners, viewport purge gas, and modified load-lock procedures to minimize condensation.

Cost Estimation

| Component | Estimated Cost |

|---|---|

| LN₂ cooling system (basic) | $10K–$25K |

| Closed-loop cryocooler | $30K–$80K |

| Temperature control electronics | $5K–$15K |

| Chamber modifications & condensation management | $5K–$10K |

| Total (LN₂ route) | $20K–$50K |

| Total (cryocooler route) | $40K–$105K |

NineScrolls can advise on cryogenic upgrade paths for our ICP and RIE etching platforms. Contact our engineering team to discuss the best cooling solution for your specific system and research needs.

Emerging Trends: Combining the Best of Both Worlds

Recent research has explored hybrid approaches that combine elements of both techniques:

Variable-temperature Bosch: Running Bosch cycles at moderately low temperatures (−20°C to −50°C) can reduce scallop depth while maintaining the robustness of fluorocarbon passivation. Studies have demonstrated that cooling to −30°C during Bosch DRIE reduced scallop amplitude by 60% while maintaining comparable etch rates.

Cryo-pulsed processes: Alternating between etch-dominant and passivation-dominant conditions at cryogenic temperatures can provide additional profile control for extreme aspect ratios.

ALE at cryogenic temperatures: Combining the self-limiting nature of atomic layer etching with cryogenic sidewall passivation is an active area of research, offering the potential for atomic-level depth control with smooth, high-aspect-ratio profiles. See our related article: Atomic Layer Etching (ALE): A Practical Guide for Research and Development.

Industry Adoption and Recent Developments

Equipment availability: Oxford Instruments’ PlasmaPro 100 Estrelas and SPTS’s Rapier series now offer integrated cryogenic chuck options as standard configurations, reducing the barrier to entry for research labs considering cryogenic capability.

Process library expansion: Beyond silicon, cryogenic etching has been demonstrated for InP (for photonic integrated circuits), SiC (for power device trenches), and even polymers (for bio-MEMS applications). The SF₆/O₂ chemistry that works well for silicon has been adapted with Cl₂ or HBr additions for III-V cryogenic etching, expanding the material palette significantly.

Throughput improvements: Recent work has demonstrated a “warm-start” cryogenic process that reduces thermal equilibration time from 10 minutes to under 3 minutes by pre-cooling the chuck during wafer loading. Combined with optimized LN₂ flow control, this improved throughput to 10–14 wafers/hour — narrowing the gap with Bosch processing.

Hybrid cryo-Bosch in production: A hybrid cryo-Bosch process for the latest generation of MEMS inertial sensors uses cryogenic etching for the final 5 μm of a 30 μm deep trench (where sidewall smoothness matters most for Q-factor) after a conventional Bosch etch for the bulk removal. This pragmatic approach captures the benefits of both techniques while maintaining acceptable throughput.

Practical Recommendations

For labs setting up cryogenic etching capability for the first time:

- Start with silicon trench etching — Use simple trench patterns (1–10 μm width) to map the parameter space: SF₆ flow, O₂ flow, ICP power, bias power, pressure, and temperature.

- Map the profile transition — At a fixed chemistry, vary the substrate temperature from room temperature down to −120°C. You will observe a clear transition from isotropic (warm) to anisotropic (cold) behavior, defining your process window.

- Optimize O₂/SF₆ ratio — This is the most sensitive knob for profile control. Too little O₂ leads to undercut; too much produces grassy or micro-masked surfaces. Typical optimal ratios are 0.05–0.15.

- Check for cryo-condensation artifacts — At very low temperatures and higher pressures, unwanted condensation can occur. Monitor for irregular surface features and adjust pressure/temperature accordingly.

- Compare with your Bosch baseline — Etch the same test structures with both processes to directly compare sidewall roughness, profile uniformity, and etch rate for your specific application.

- Monitor thermal budget — Track the total time your devices spend at cryogenic temperatures. For most materials and device structures, the thermal budget of cryo-etching is benign, but verify for your specific film stacks.

Conclusion

Cryogenic plasma etching is not a replacement for the Bosch process — it is a complementary technique that excels in applications where sidewall smoothness, process simplicity, and clean passivation matter most. As photonics, quantum devices, and advanced MEMS push the boundaries of what conventional DRIE can deliver, cryogenic etching is poised to become an increasingly important tool in the researcher’s arsenal.

Understanding the trade-offs between these two approaches allows you to select the optimal process for your specific device requirements — or to combine elements of both for next-generation fabrication challenges.

Related Articles in This Series

- Deep Reactive Ion Etching (DRIE) — the Bosch process explained in depth

- Atomic Layer Etching (ALE) — a practical guide for precision etch applications

- The Selectivity Challenge — achieving ultra-high etch selectivity in modern plasma processes

Frequently Asked Questions

What is the main advantage of cryogenic etching over the Bosch process?

The primary advantage is sidewall smoothness. Cryogenic etching produces sidewall roughness below 10 nm RMS, compared to 50–200 nm scallop depths from the Bosch process. This is critical for photonic waveguides, MEMS resonators, and quantum devices where surface quality directly impacts performance. Additionally, cryo-etching uses simpler chemistry (SF₆/O₂ only) and the passivation layer desorbs on warming, eliminating the need for post-etch polymer stripping.

Can I convert my existing ICP-RIE system for cryogenic etching?

Yes. Many labs retrofit existing ICP-RIE systems for cryogenic capability. The main upgrade is a substrate cooling system — either liquid nitrogen direct cooling ($10K–$25K) or a closed-loop cryocooler ($30K–$80K). You also need helium backside cooling, temperature sensors, and condensation management. The total retrofit cost is typically $20K–$50K for the LN₂ route or $40K–$105K for the cryocooler route.

What aspect ratios can cryogenic etching achieve?

Cryogenic etching currently achieves aspect ratios exceeding 20:1, with ongoing improvements pushing this further. The Bosch process holds the advantage for extreme aspect ratios (> 30:1) and very deep etches (> 200 μm). For many MEMS and photonic applications where aspect ratios of 10–20:1 are sufficient, cryogenic etching provides equivalent or superior results with the added benefit of smooth sidewalls.

Is cryogenic etching suitable for production or only for R&D?

Cryogenic etching is increasingly production-viable. Leading equipment vendors now offer production-qualified cryogenic modules. Throughput of 8–14 wafers/hour is achievable with optimized processes, and wafer-to-wafer depth uniformity of ±2% has been demonstrated. Hybrid cryo-Bosch approaches — using Bosch for bulk removal and cryo for the final critical etch — are already in production at major MEMS foundries.

What materials can be etched with cryogenic processes beyond silicon?

Beyond silicon, cryogenic etching has been demonstrated for InP (photonic integrated circuits), SiC (power device trenches), and polymers (bio-MEMS). The SF₆/O₂ chemistry for silicon has been adapted with Cl₂ or HBr additions for III-V compound semiconductors. Niobium for superconducting quantum devices is another growing application. The material palette continues to expand as process recipes are developed for new material systems.

References and Further Reading

- Oehrlein, G. S., et al. “Future of plasma etching for microelectronics: Challenges and opportunities.” J. Vac. Sci. Technol. B 42, 041501 (2024). doi:10.1116/6.0003579

- Dussart, R., et al. “Plasma cryogenic etching of silicon: from the early days to today’s advanced technologies.” J. Phys. D: Appl. Phys. 47, 123001 (2014).

- de Boer, M. J., et al. “Guidelines for etching silicon MEMS structures using fluorine high-density plasmas at cryogenic temperatures.” J. Microelectromech. Syst. 11, 385 (2002).

- Henry, M. D., et al. “ICP cryogenic reactive ion etching of silicon: A comparison with the Bosch process.” J. Micromech. Microeng. 19, 065014 (2009).

- Wu, B., et al. “High aspect ratio silicon etch: A review.” J. Appl. Phys. 108, 051101 (2010).