Hard Mask Processing: Materials, Integration, and Pattern Transfer Strategies

By NineScrolls Engineering · 2026-04-23 · 22 min read · Process Integration

Target Readers: Semiconductor and MEMS process engineers, integration engineers, photonics and compound-semiconductor researchers, and cleanroom lab managers selecting mask strategies for deep or selectivity-limited etching. Newcomers will benefit from the fundamentals and material selection matrix; experienced engineers can skip to the integration flows, pattern transfer budgets, and the removal/strip troubleshooting reference.

TL;DR

- A hard mask is an inorganic (oxide, nitride, metal, or amorphous carbon) film inserted between the photoresist and the substrate to survive etch conditions where resist alone would erode, deform, or offer insufficient selectivity.

- Material choice is a selectivity × deposition × removal trade-off — SiO2 and SiN are versatile and cheap, metals (Cr, Ti, TiN, W) give extreme selectivity for deep Si and III–V etches, Al2O3 ALD films offer pinhole-free sub-10 nm masks, and spin-on or CVD amorphous carbon (ACL/APF) enables tall, high-aspect-ratio stacks like 3D NAND.

- The full process flow is deposit hard mask → coat resist → expose/develop → transfer pattern into hard mask → strip resist → etch substrate through hard mask → remove hard mask. Each handoff has its own selectivity, CD-budget, and defect risk.

- Hard masks extend the reach of lithography: they let thin EUV/e-beam resists pattern deep silicon, GaN, SiC, and dielectric stacks that would otherwise exceed the resist's etch budget by 5–50×.

- Removing the hard mask without damaging the patterned structure is often the hardest step — wet, dry, and CMP options each carry their own selectivity and topography penalties.

1) What Is a Hard Mask and Why It Exists

In a single-layer lithography flow, photoresist serves as both the imaging layer and the etch mask. That works when the etch depth is shallow, the required selectivity is modest, and the resist is thick enough to absorb sidewall erosion without loss of critical dimension. As soon as any of those conditions break — deeper etches, higher plasma bias, more aggressive chemistries, or resist too thin to survive (EUV, high-resolution e-beam) — a hard mask becomes the only practical answer.

A hard mask is a film of inorganic or carbon-based material deposited beneath the resist. The resist pattern is first transferred into the hard mask using a short, highly selective etch, the resist is stripped, and the hard mask then serves as the mask for the main substrate etch. Because the hard mask is chemically distinct from the substrate and typically 2–50× more resistant to the main etch chemistry than any photoresist, it preserves CD and profile over etch depths that would destroy a bare resist mask.

1.1 When Resist Alone Is Not Enough

The decision to introduce a hard mask almost always comes down to one of five drivers:

- Insufficient selectivity. Chlorine-based Si etches (Cl2/HBr), BCl3-based III–V etches, and fluorocarbon oxide etches all erode photoresist at rates comparable to the target material. Selectivity to resist typically tops out at 2–4:1, which is inadequate for deep features.

- Resist too thin to survive. EUV resists are <60 nm, and high-resolution e-beam resists like HSQ or PMMA are often 50–150 nm — far below the thickness needed for even moderate etch depths.

- High-temperature or high-bias plasma. Resist softens, reflows, or carbonizes above ~150 °C and loses profile integrity under high ion bombardment. Metals and oxides do not.

- Chemistry-incompatible etch. Some etch chemistries (hot HCl vapor, Cl2/BCl3 for sapphire, HBr with high O2 addition) attack organic resist faster than the target substrate.

- High-aspect-ratio / 3D integration. Channel holes in 3D NAND, deep Si vias, and GaN/SiC power-device mesas routinely need mask budgets beyond what a single resist layer can provide — hard masks are mandatory.

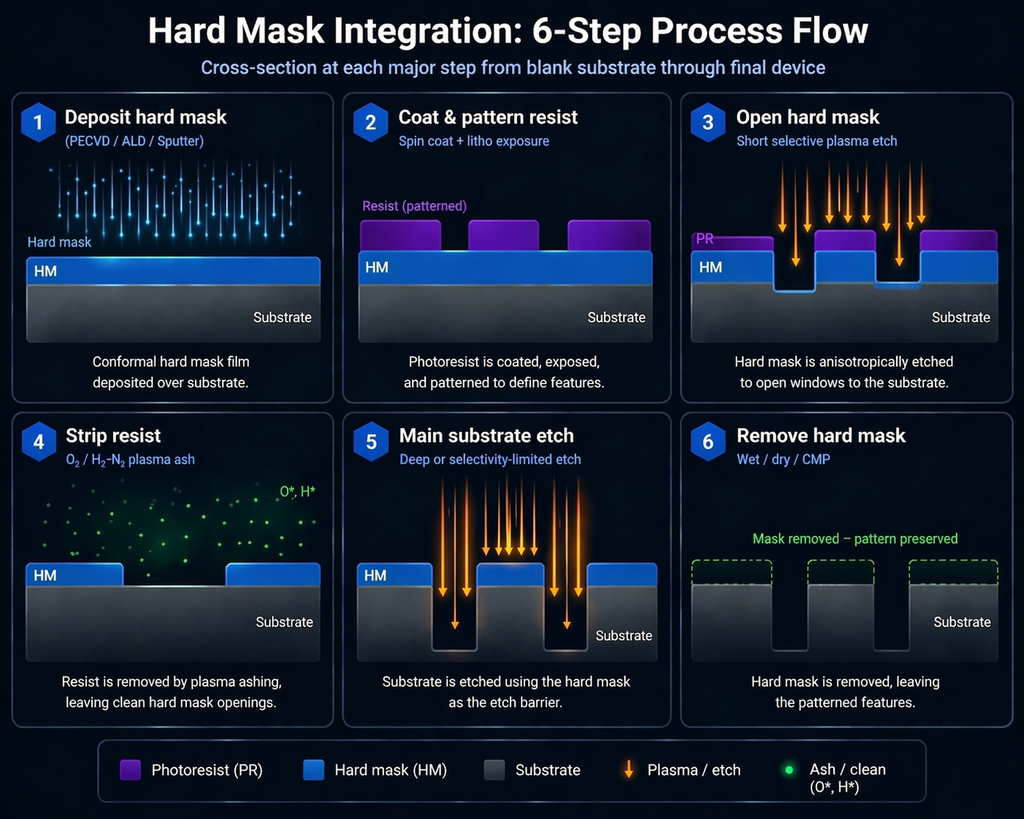

Figure 1: Six-step hard mask integration flow. Each panel is a cross-section at that process step — the hard mask (blue) inherits the resist image, survives the main substrate etch long after the resist is gone, and is removed once the pattern is transferred.

1.2 Hard Mask vs Soft Mask vs Multi-Layer Stacks

It is useful to place hard masks on a continuum of mask architectures:

- Single-layer resist (soft mask): Fastest flow, fewest process steps, lowest cost — used wherever the etch depth and selectivity allow it.

- Bilayer (resist over BARC or planarizing layer): Still a soft mask, but improves reflectivity control and CD at the cost of one extra etch step.

- Tri-layer / multi-layer (resist / Si-ARC / spin-on carbon): The Si-ARC acts as a thin hard mask, and the spin-on carbon (SOC) underneath is a sacrificial planarizing layer. Common in advanced logic for EUV patterning.

- Conventional hard mask (CVD/sputter/ALD inorganic film): Inorganic or amorphous carbon, 10–500 nm thick, for deep or selectivity-limited etches.

- Dual hard mask (metal hard mask over dielectric hard mask): Used where neither layer alone survives the full etch budget — e.g., TiN over SiN for extreme-aspect-ratio contact etches.

2) Hard Mask Materials: Selection Matrix

There is no universal "best" hard mask. The choice depends on the substrate being etched, the etch chemistry, the required selectivity, the minimum feature size, and the available removal method. The table below compares the workhorse materials used in semiconductor, MEMS, photonics, and compound-semiconductor processing.

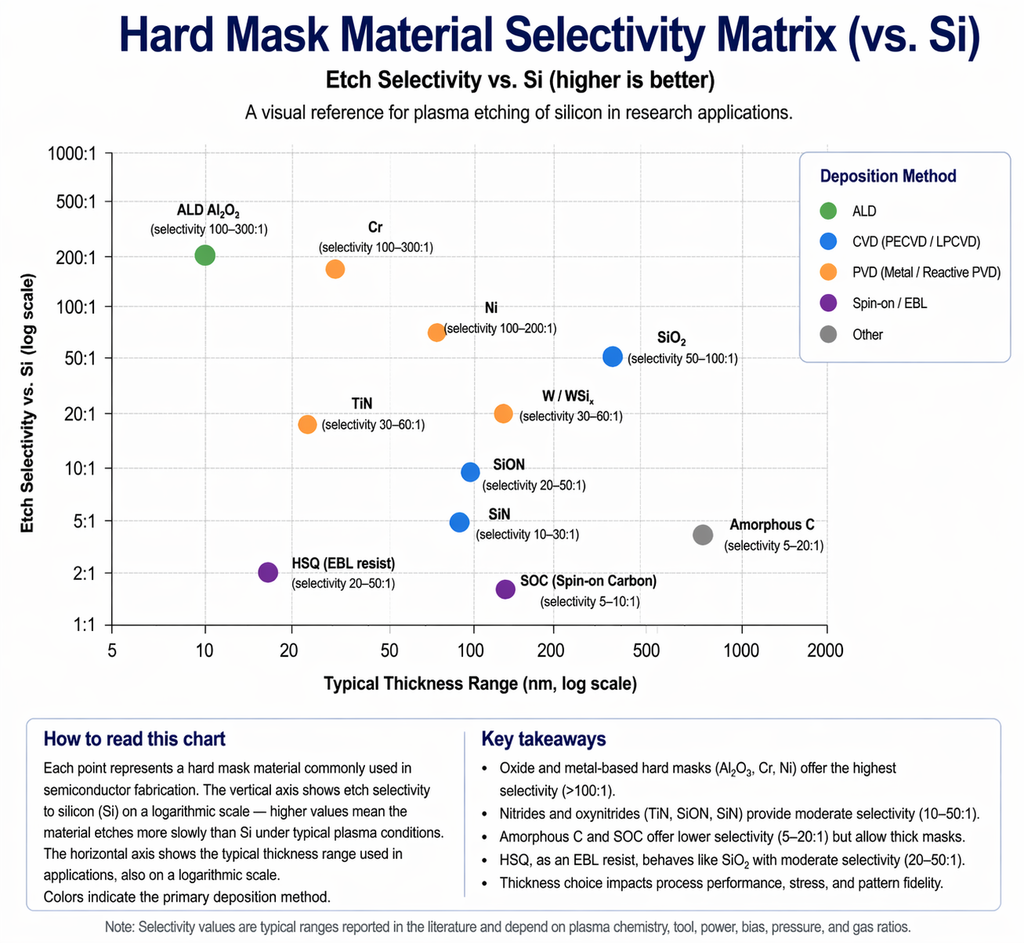

Figure 2: Material selectivity map. Thickness range (x-axis, log) versus typical Si-etch selectivity (y-axis, log). Bubble color encodes deposition method; range boxes show the practical process window each material occupies. ALD Al2O3 and Cr own the thin/high-selectivity corner; amorphous carbon and SOC dominate the thick/lower-selectivity regime.

| Material | Typical Deposition | Thickness | Best-Match Etch | Selectivity* | Removal |

|---|---|---|---|---|---|

| SiO2 | PECVD, thermal, sputter | 30–500 nm | Si (Cl2/HBr/SF6), III–V | 50–150:1 (Si) | BOE, dilute HF, CHF3 RIE |

| SiNx / SiON | PECVD, LPCVD | 30–300 nm | SiO2, Si, polymer etch | 10–30:1 (SiO2) | Hot H3PO4, CF4/O2 |

| Al2O3 | ALD (TMA/H2O) | 5–50 nm | Deep Si (SF6/Bosch), GaN, SiC | >100:1 (Si); >30:1 (GaN) | BCl3/Cl2 plasma, hot KOH or dilute HF |

| Cr | Sputter, e-beam evap. | 10–100 nm | Deep Si (SF6, Bosch), quartz | >500:1 (Si w/ SF6) | Ceric ammonium nitrate wet etch |

| Ni | e-beam evap., liftoff | 20–150 nm | Deep Si, SiC, diamond | >200:1 (Si); >50:1 (SiC) | Dilute HNO3 or FeCl3 |

| TiN | Sputter, ALD, MOCVD | 10–80 nm | Contact/via dielectric etch | >20:1 (SiO2, low-k) | SC-1, dilute H2O2/NH4OH, Cl2 plasma |

| W / WSix | Sputter, CVD | 20–150 nm | Oxide, nitride, DRAM capacitor | >30:1 (oxide) | H2O2 wet etch, SF6 plasma |

| Amorphous C (ACL/APF) | PECVD (C3H6, CH4) | 300 nm–2 μm | 3D NAND channel, deep oxide/nitride | >4:1 (ONO stack); >10:1 (oxide) | O2 plasma ash |

| Spin-on Carbon (SOC) | Spin coat + cure | 100–400 nm | Tri-layer EUV/ArF integration | >3:1 (oxide, Si-ARC transfer) | O2 plasma ash |

| HSQ (as hard mask) | Spin coat + e-beam expose | 20–200 nm | Si, III–V nanostructures | 5–10:1 (Si) | Dilute HF |

*Selectivity values are representative ranges under optimized recipes — real-world performance depends strongly on chamber, bias, pressure, and loading.

2.1 Dielectric Hard Masks (SiO2, SiN, SiON)

Silicon oxide, silicon nitride, and oxynitride are the default starting point for most hard mask designs. They deposit easily by PECVD, they tolerate moderate thermal budgets, they pattern cleanly in fluorocarbon chemistry, and they open/remove with well-established wet and dry recipes. Selectivity to silicon under Cl2/HBr is typically 50:1 or better for SiO2, which is enough for most MEMS and moderate-depth device work.

SiN adds several benefits over SiO2: higher density (>3.0 g/cm3), better mechanical rigidity, and much lower etch rate in HF-based chemistry — useful when the underlying substrate is SiO2 and the wet clean cannot attack the mask. SiON lets you tune optical properties for anti-reflective applications in addition to acting as a mask.

2.2 Metal Hard Masks (Cr, Ni, Ti, TiN, Al, W)

Metals offer the highest selectivity available for deep Si, compound-semiconductor, and quartz etching. Under SF6-based Si etching, Cr and Ni selectivity can exceed 500:1 — enabling >100 μm silicon etches using a 50 nm mask. For III–V (GaN, InP) and SiC, Ni is a frequent mask of choice because it is non-volatile in Cl2-based chemistry while the substrate etches readily.

The trade-off with metals is contamination. Any sputtered residue of Cr, Ni, or Cu on the sidewalls or field area will cause micromasking (grass/pillars in the substrate) and deep-level trap formation in active devices. Integration rules typically segregate metal-hard-mask tools to dedicated chambers, and the removal step is a required wet clean even if the mask film itself is thin.

2.3 ALD Al2O3 — The Sub-10 nm Workhorse

For nanoscale patterning where a dielectric or metal hard mask would be too thick to define with a thin e-beam resist, ALD Al2O3 has become the dominant choice. A 5–20 nm conformal, pinhole-free Al2O3 layer provides selectivity >100:1 to Si under SF6, enables aspect ratios >20:1 in DRIE, and patterns cleanly in BCl3/Cl2 plasma. The ALD conformality also makes Al2O3 uniquely suited for double-patterning spacer processes (SADP/SAQP) where a sacrificial mandrel is coated with Al2O3 and the mandrel is selectively stripped to leave spacer lines at half-pitch.

2.4 Amorphous Carbon / Advanced Patterning Films

Extreme-aspect-ratio etches — especially 3D NAND channel holes through 300+ alternating oxide/nitride layers, and deep DRAM capacitor etches — require mask thicknesses approaching 1–2 μm with minimal line-edge roughness. Dielectric and metal masks at that thickness are hard to pattern with thin resist and are difficult to remove without damage. The industry answer is amorphous carbon layer (ACL), also sold commercially as APF (Advanced Patterning Film): a dense, highly cross-linked sp2/sp3 carbon deposited by PECVD from hydrocarbon precursors.

Key properties of amorphous carbon hard masks:

- Deposition rate 100–500 nm/min at 300–500 °C, density 1.7–2.0 g/cm3

- Selectivity to oxide/nitride >4:1, to Si >10:1

- Low stress, patterns cleanly in HBr/O2 or N2/O2

- Removable by O2 plasma ash with no wet step — a major advantage over metal or oxide masks

- Transparent to alignment-mark inspection at visible wavelengths (newer low-hydrogen variants)

3) Deposition Methods and Film Quality

The deposition method determines the hard mask's density, stress, conformality, defectivity, and compatibility with underlying layers. A summary of the main options:

| Method | Typical Films | Temperature | Conformality | Key Advantage |

|---|---|---|---|---|

| PECVD | SiO2, SiN, SiON, a-C | 200–400 °C | Moderate (70–90%) | High rate, tunable stress, process flexibility |

| LPCVD | SiN (stoichiometric), poly-Si | 700–800 °C | Excellent (>95%) | Dense, low H-content, batch throughput |

| ALD | Al2O3, HfO2, TiO2, TiN | 80–300 °C | >99%, pinhole-free | Ångström thickness control, HAR conformality |

| Sputter / PVD | Cr, Ni, Ti, TiN, W, SiO2 | 25–200 °C | Poor (30–60%) | Low temperature, clean metals, simple targets |

| Thermal evap. | Cr, Ni, Au, Al | 25–100 °C | Line-of-sight | Best for liftoff-defined metal masks |

| Spin-on | HSQ, SOC, Si-ARC | 25 °C spin, 200–400 °C cure | Planarizing | Fills topography, no vacuum step |

3.1 Stress and Adhesion Considerations

A hard mask that delaminates, cracks, or bows the wafer is useless regardless of its etch selectivity. Film stress must be controlled to < ±300 MPa for most applications, and < ±100 MPa for wafer-bow-sensitive steps like EUV lithography or thin MEMS membranes. PECVD SiN stress is tunable from −1 GPa (compressive, high HF/LF ratio) to +500 MPa (tensile, low frequency) — a capability unique to PECVD. ALD Al2O3 stress is typically tensile (+100 to +400 MPa) and weakly dependent on process.

Adhesion is the other chronic failure mode. For metals on oxide, a thin (<5 nm) Ti or Cr adhesion layer is almost always required. For oxides on metals, an in-situ pre-deposition plasma clean (Ar or H2) is the usual solution. If adhesion loss is observed only after the main etch, the likely cause is sidewall undercut — a problem to be solved by tightening the pattern-transfer selectivity rather than by the adhesion layer.

4) The Hard Mask Process Flow

A typical hard mask integration breaks down into six sequential operations:

- Hard mask deposition. Establish the target thickness with on-wafer uniformity < ±3%, stress within budget, and defect density below the device's yield threshold.

- Resist coat and pattern. Apply photoresist or e-beam resist directly on the hard mask (or through an anti-reflective coating). Expose, develop, and inspect CD.

- Hard mask open (pattern transfer). Transfer the resist pattern into the hard mask with a short, highly selective plasma etch. The goal is to minimize CD loss, sidewall roughness, and substrate damage.

- Resist strip. Remove the remaining photoresist in O2 plasma (or H2/N2 for metal-sensitive substrates). See our Plasma Stripping & Ashing Guide for detailed parameter ranges.

- Main etch through the hard mask. Execute the deep or selectivity-limited substrate etch with the hard mask now serving as the only image carrier.

- Hard mask removal. Strip or planarize the hard mask without damaging the patterned substrate, and perform the post-etch clean (see Post-Etch Cleaning & Residue Removal).

4.1 Pattern Transfer from Resist into Hard Mask

This is usually the most delicate step because a thin resist (50–300 nm) must survive the etch into the hard mask. The target selectivity is resist-to-hard-mask at least 1:1, ideally 2:1, and the etch should stop cleanly on the layer beneath the mask (substrate or BARC).

Representative starter recipes:

- SiO2 (80–150 nm) with CHF3/Ar: 50 mTorr, 150 W RIE bias, resist:oxide selectivity ~1:1 — adjust CHF3/O2 ratio to tune sidewall passivation.

- SiN (60–200 nm) with CF4/O2: 30 mTorr, 100 W, 10% O2, resist:SiN selectivity ~0.8–1.2:1.

- Cr (20–100 nm) with Cl2/O2: 10 mTorr, 200 W ICP / 50 W bias, selectivity ~1:1; endpoint by OES on CrO emission.

- Al2O3 (5–20 nm) with BCl3/Cl2: 5 mTorr, 500 W ICP / 50 W bias; selectivity >3:1 to resist for thin ALD films.

- Amorphous carbon (300 nm–1 μm) with HBr/O2 or N2/O2: 10 mTorr, 200 W ICP / 100 W bias; photoresist-to-carbon selectivity is inherently low (<0.5:1), which is why ACL integration almost always uses a thin Si-ARC or metal hard mask on top of the carbon.

Line-edge roughness (LER) inherited from the resist is amplified slightly during the transfer — typical amplification factor 1.1–1.4×. If the main etch is aspect-ratio sensitive, budget additional LER for the second transfer into the substrate.

4.2 Main Etch Through the Hard Mask

Once the resist is stripped, the hard mask carries the pattern alone. The main etch can now use chemistries and ion energies that would have destroyed the resist in seconds. The hard mask's etch budget — thickness divided by hard-mask-to-substrate selectivity — must cover the full etch depth plus a margin for over-etch and loading non-uniformity.

A worked example: a 100 μm deep Si trench etched with SF6-based cryogenic RIE has Si-to-SiO2 selectivity ~100:1. A 1.5 μm SiO2 hard mask provides an etch budget of 150 μm — adequate with 50% margin. If instead a Ni hard mask is used at 500:1 selectivity, just 250 nm of Ni suffices for the same depth.

For high-aspect-ratio etches, the hard mask top corners also erode due to ion-angular-distribution spread — this is the faceting failure mode. A more sputter-resistant mask (C, Al2O3, or W) or a mask with a sacrificial top layer solves faceting without changing the main etch recipe.

5) Hard Mask Removal

Hard mask removal is often the step where a process that looked good in early development runs into yield trouble. The ideal removal chemistry has infinite selectivity to the patterned substrate, produces no particles, leaves no residual contamination, and adds minimal cycle time. In practice, compromises are unavoidable.

5.1 Removal Strategy by Mask Type

| Hard Mask | Primary Removal | Alternative | Main Risk |

|---|---|---|---|

| SiO2 | Dilute HF (0.5–5%) or BOE | CHF3/CF4 plasma etch-back | Attacks any exposed SiO2 in the device |

| SiN | Hot H3PO4 (160 °C) | CF4/O2 downstream plasma | Slow; process bath contamination; attacks thin oxides |

| Al2O3 | Hot KOH (80 °C) or dilute HF | BCl3/Cl2 plasma | KOH attacks Si; HF attacks SiO2 |

| Cr | Ceric ammonium nitrate | Cl2/O2 plasma | Cr contamination risk for active devices |

| Ni | Dilute HNO3, FeCl3 | Ion milling | Nickel silicide formation above 300 °C |

| TiN / W | H2O2-based wet, SC-1 | SF6 plasma | Selectivity to underlying dielectric |

| Amorphous C / SOC | O2 plasma ash | O2/N2 downstream | Oxidizes any exposed Cu, Co, or low-k |

| HSQ | Dilute HF | CHF3 etch-back | Often intentionally retained as device layer |

5.2 CMP as a Removal Path

For some advanced integrations (metal gate, contact landing pad) the hard mask is not removed chemically but planarized off via chemical mechanical polishing. CMP is effective only when the hard mask is flush with a stop layer (polish stops on nitride or metal) and when the wafer topography is tolerable for the slurry chemistry. CMP is the only realistic option for thick (>1 μm) refractory metal masks because their wet etch rates are too slow.

6) Applications Across Device Classes

6.1 Logic and Memory (FinFET, GAA, 3D NAND, DRAM)

Advanced logic nodes use multi-layer hard mask stacks for every critical patterning step. A typical FinFET fin etch uses a TiN/oxide/amorphous-carbon triple stack: TiN is the ultimate etch mask for the silicon fin, the oxide defines the TiN pattern, and the amorphous carbon lets the EUV resist define the oxide. Each layer is individually thin enough to be patterned, and the stack as a whole survives the fin etch with CD control <1 nm 3σ.

3D NAND channel-hole etch is the extreme case: >8 μm deep through hundreds of alternating SiO2/Si3N4 layers, aspect ratio >60:1. The mask is 1.5–2 μm of amorphous carbon, patterned by a thinner oxide/SiARC/resist stack, and removed by O2 ash. See our guide on ultra-high etch selectivity for more on this regime.

6.2 MEMS and Deep Silicon Etching

Silicon DRIE (Bosch, cryogenic) for MEMS devices, through-silicon vias (TSVs), and microfluidic channels relies on SiO2 or metal hard masks for etch budgets up to several hundred micrometers. A 2–4 μm PECVD SiO2 mask is the workhorse for 200–500 μm Bosch etches; Ni or Cr masks are used when SiO2 thickness would introduce excessive stress or where the SiO2 must remain on the device.

6.3 Compound Semiconductors (GaN, SiC, GaAs, InP)

Wide-bandgap and III–V materials often require Cl2-based chemistry with high DC bias, where photoresist selectivity is 1:1 at best. Ni and SiO2 hard masks are the standard; ALD Al2O3 is increasingly used for fine-line GaN HEMTs. For more detail on etching these materials, see the Wide-Bandgap Semiconductor (GaN, SiC) Fabrication Guide and the III–V Compound Semiconductor Etching Guide.

6.4 Photonics, Quartz, and Nanofabrication

Silicon photonics waveguides, quartz photomask blanks, and e-beam-defined nanostructures share a common need: smooth, vertical sidewalls over depths larger than the resist can sustain. HSQ (as self-masking e-beam resist) and ALD Al2O3 dominate sub-100 nm features; Cr and SiO2 are standard for microscale waveguides and gratings.

7) Integration Challenges and Troubleshooting

Process problems specific to hard mask flows tend to cluster around a handful of recurring failure modes — most visible in cross-section SEM.

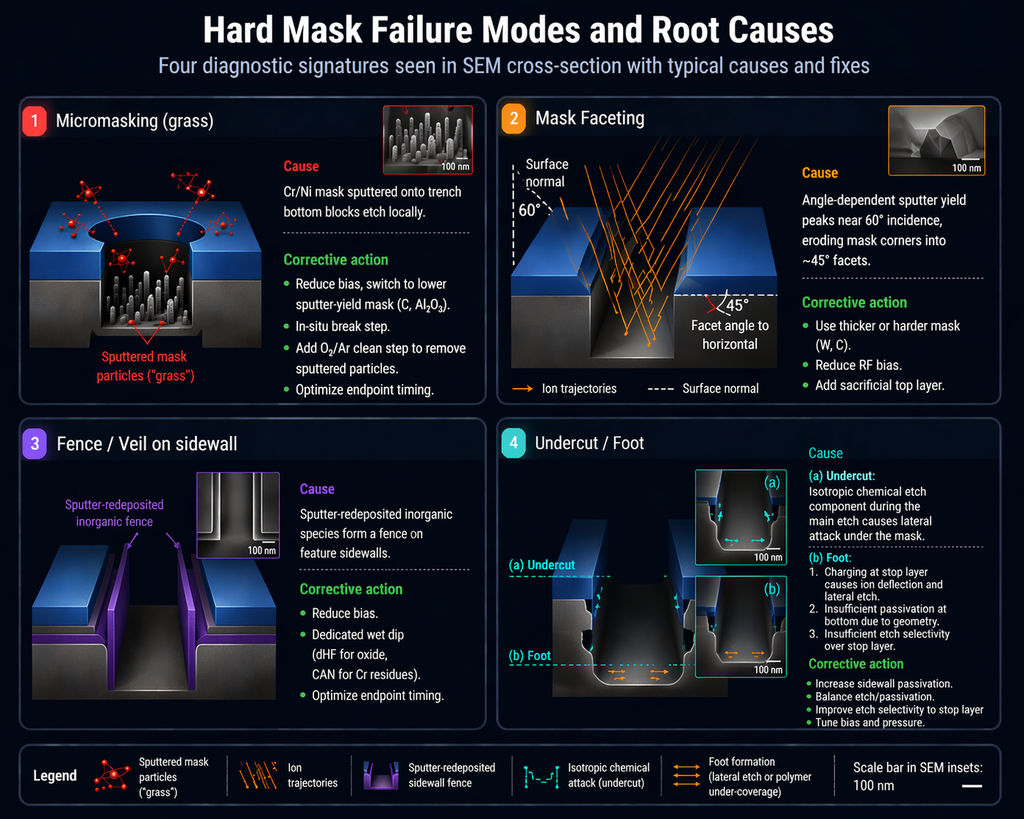

Figure 3: Four common hard mask failure modes. Micromasking (grass) from sputtered mask particles, faceting at the mask top corner, sidewall fences from redeposited inorganic mask, and undercut or foot at the mask-substrate interface — each with its own root cause and corrective action.

The table below maps the symptom to the most likely cause, a diagnostic to confirm it, and the corrective action.

| Symptom | Likely Cause | Diagnostic | Corrective Action |

|---|---|---|---|

| Micromasking (grass/pillars) in substrate | Sputtered hard-mask material redeposited as non-volatile residue | SEM; EDX on grass — Cr, Ni, Ti signal confirms mask sputter | Reduce bias power; increase passivation; switch to softer mask (SiO2 or Al2O3); add in-situ clean step between resist strip and main etch |

| Hard mask undercut / foot | Pattern-transfer chemistry not anisotropic enough, or wet removal attacks interface | XSEM at interface; compare pre- and post-removal CD | Add sidewall passivation to transfer recipe; use plasma-based mask removal instead of wet |

| Mask delamination / blistering | Stress too high; poor adhesion; trapped moisture at interface | Optical inspection; wafer-bow measurement | Add Ti/Cr adhesion layer; anneal after deposition; retune deposition stress |

| Faceting of mask top corners | Ion-angle spread erodes the corner at 45° | Cross-section SEM showing rounded mask top | Thicker or harder mask (C, W, Al2O3); reduce bias; add sacrificial top layer |

| Fence / veil on sidewalls after mask strip | Sputter-redeposited mask on feature sidewalls | SEM + EDX confirms inorganic composition | See post-etch cleaning guide; reduce bias; add selective wet dip |

| CD loss after mask removal | Removal chemistry also attacks the patterned substrate | CD-SEM pre and post removal | Switch to more selective removal; time-limit wet etches; consider CMP |

| Metal contamination in active area | Residual Cr, Ni, or Cu from metal hard mask | TXRF or VPD-ICPMS on wafer surface | Extended SC-1 or dedicated wet clean; tool segregation for metal-hard-mask flows |

Related Articles

- Post-Etch Cleaning & Residue Removal — handle the residues that hard-mask flows leave behind

- Lithography Process Integration Guide — full integration context for the resist-to-hard-mask handoff

- Ultra-High Etch Selectivity — the regime where hard masks are mandatory

- Atomic Layer Deposition (ALD) Comprehensive Guide — for sub-10 nm Al2O3 / HfO2 mask layers

- PECVD Complete Guide — SiO2, SiN, and amorphous carbon deposition recipes

- Plasma Stripping & Ashing Guide — O2 and H2/N2 strip chemistry for resist and carbon masks

8) Frequently Asked Questions

When should I use a hard mask instead of a thicker photoresist?

Use a hard mask when any of the following is true: (1) the required etch depth divided by the resist-to-substrate selectivity exceeds the practical resist thickness (typically >2–3 μm); (2) the substrate etch chemistry attacks resist as fast as the substrate (Cl2/HBr on Si, BCl3 on GaN, high-bias oxide etches); (3) your resist is thin by design (EUV, high-resolution e-beam) and cannot be thickened without destroying resolution; or (4) the process temperature exceeds about 150 °C, where resist softens or carbonizes. If the etch is shallow (<1 μm) and the selectivity is above 3:1, stick with resist — you save two deposition, one patterning, and one removal step.

How thick should a hard mask be?

Start from the etch budget equation: required thickness ≥ (etch depth / hard-mask-to-substrate selectivity) × (1 + over-etch margin). Typical over-etch margins are 30–50%. For a 100 μm Si Bosch etch at Si:SiO2 ~150:1, minimum SiO2 is 100/150 = 0.67 μm, and 1.0–1.5 μm is standard. For nanoscale etches, aim for the thinnest mask that still survives the etch — every extra nanometer of mask thickness worsens aspect ratio, ion shadowing, and pattern-transfer CD loss. An ALD Al2O3 mask at 10–20 nm is often the right answer for deep features at sub-100 nm CD.

What is the difference between a hard mask and a sacrificial layer?

A hard mask is the imaging layer — it carries the pattern during the main etch. A sacrificial layer is any film whose purpose is temporary (planarization, stress relief, stop layer, release layer) and is not required to hold a pattern. They can overlap: a spin-on carbon layer in a tri-layer EUV stack is both a planarizing sacrificial layer and, briefly, a hard mask during the substrate etch. The distinction matters when specifying film quality: hard masks must meet tight thickness, stress, and defectivity specifications; pure sacrificial layers often do not.

Why is amorphous carbon used instead of SiO2 for 3D NAND?

Three reasons. First, the etch budget: 3D NAND channel holes now penetrate >8 μm of alternating oxide/nitride at aspect ratio >60:1. The required SiO2 mask thickness would be close to 2 μm, which is hard to pattern with a thin EUV or ArF resist. Amorphous carbon delivers comparable selectivity at lower density and can be thicker without deforming wafer bow. Second, ion sputter resistance: amorphous carbon facets more slowly under high-energy fluorocarbon plasma than SiO2 at the same thickness. Third, removal: O2 plasma ash strips carbon cleanly with no wet step and no attack on the oxide/nitride stack — a significant yield advantage over the HF dip that SiO2 masks would require.

Can I use a metal hard mask in a CMOS flow?

Only with strict contamination control. Metals like Cr, Ni, Cu, and Fe are lifetime killers in Si MOS devices — even parts-per-billion residuals degrade minority-carrier lifetime and increase junction leakage. If a metal hard mask is unavoidable (for example, to etch deep TSVs), the standard practice is: dedicate the deposition, etch, and strip tools to the metal-hard-mask flow, separate them from front-end-of-line equipment, and perform a rigorous post-strip clean (typically SC-1 + dilute HF + TXRF verification) before the wafer can return to active-device processing. TiN and W are more forgiving because their diffusion into Si is limited compared to Cr/Ni/Cu, which is why they dominate CMOS hard-mask use cases.

How do I remove a hard mask without rounding or damaging the substrate features?

Match the removal chemistry to the specific mask-to-substrate system and time it against the mask thickness, not the visual endpoint. For SiO2 masks on Si, a buffered HF dip with in-line thickness monitoring is standard; for Cr on Si, ceric ammonium nitrate timed to the nominal Cr thickness + 10% limits over-etch. For nanoscale or high-aspect-ratio features, plasma removal (BCl3/Cl2 for Al2O3, O2 for carbon) often outperforms wet because it is anisotropic and avoids capillary forces that can collapse fine structures. Always measure the post-removal profile by cross-section SEM or AFM before qualifying the process — visual top-down inspection does not reveal sidewall damage or top-corner rounding.

What causes micromasking ("black silicon" or grass) when using a metal hard mask?

Micromasking is caused by sub-micrometer particles of the hard mask material being sputtered off during etching and redeposited on the substrate, where they locally block etching and create forests of sharp silicon pillars. It is most common with Cr, Ni, and Ti masks under high-bias etching. Prevention strategies: lower the RF bias (reduces sputter yield), add a thin sacrificial oxide on top of the metal to reduce direct ion impact, introduce an in-situ break step between resist strip and main etch to remove early redeposition, or switch to a lower-sputter-yield mask (C, Al2O3, or SiO2). If micromasking is already present, a short dip in metal-specific wet etchant followed by a KOH or SF6 grass-removal etch usually recovers the wafer.

NineScrolls Hard Mask Processing Solutions

NineScrolls supplies the full equipment chain behind every hard mask flow: PECVD for SiO2, SiN, and amorphous carbon deposition; ALD for sub-10 nm Al2O3 and HfO2 masks; sputter deposition for Cr, Ti, TiN, and W; ICP etchers for high-selectivity pattern transfer; RIE systems for mask opening and etch-back; and plasma strippers for resist and carbon-mask removal. Our process engineers can review your target device, substrate, and etch budget and recommend the complete mask stack and integration flow.