Lithography Process Integration: From Substrate Preparation to Pattern Transfer

By NineScrolls Engineering · 2026-03-16 · 15 min read · Nanotechnology

Target Readers: Lithography process engineers, integration engineers, cleanroom technicians, PIs/lab managers, and technical decision-makers building or optimizing patterning process flows. Newcomers will benefit from the end-to-end flow overview and parameter tables; experienced engineers can skip to the process interface sections, CD control strategies, and troubleshooting guidance.

TL;DR

- Lithography process integration is the discipline of optimizing not just individual steps but the interfaces between them — each step's output is the next step's input, and errors compound through the flow.

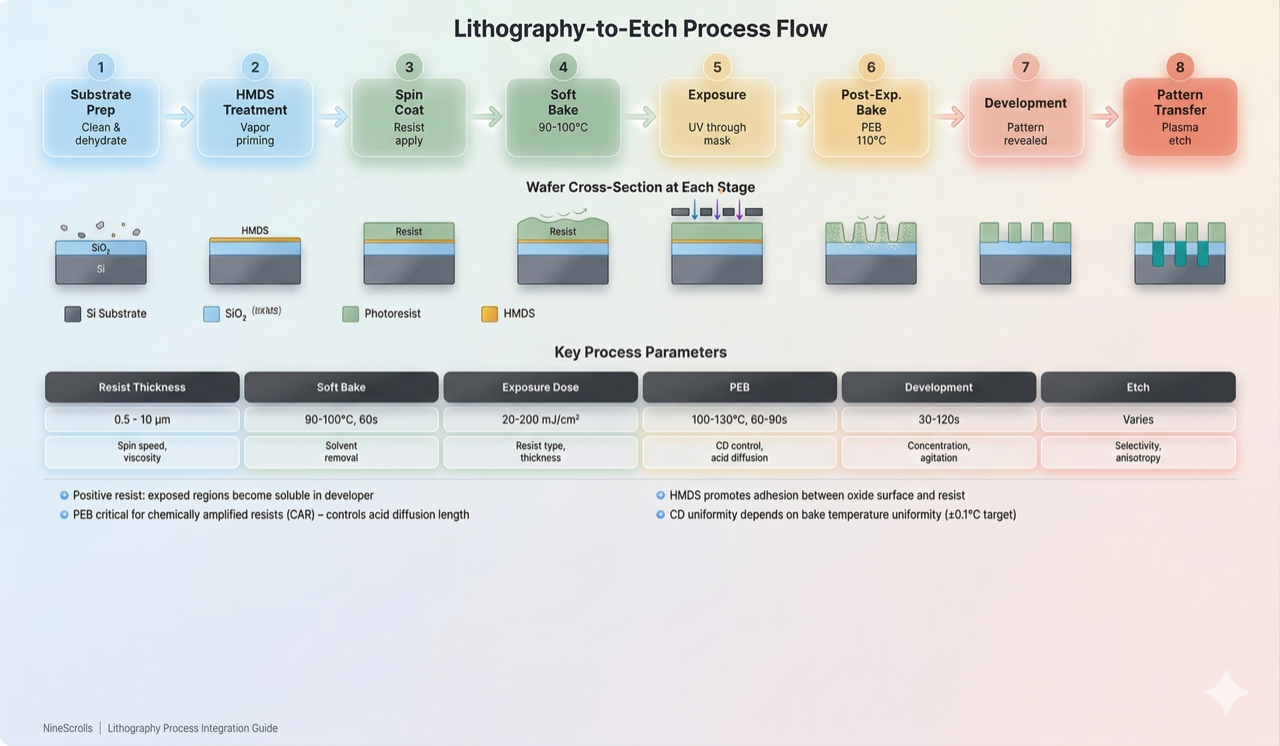

- The full flow is: substrate cleaning → HMDS priming → spin coating → soft bake → alignment & exposure → PEB → development → hard bake → etch pattern transfer → resist strip. Omitting or mis-sequencing any step degrades final pattern fidelity.

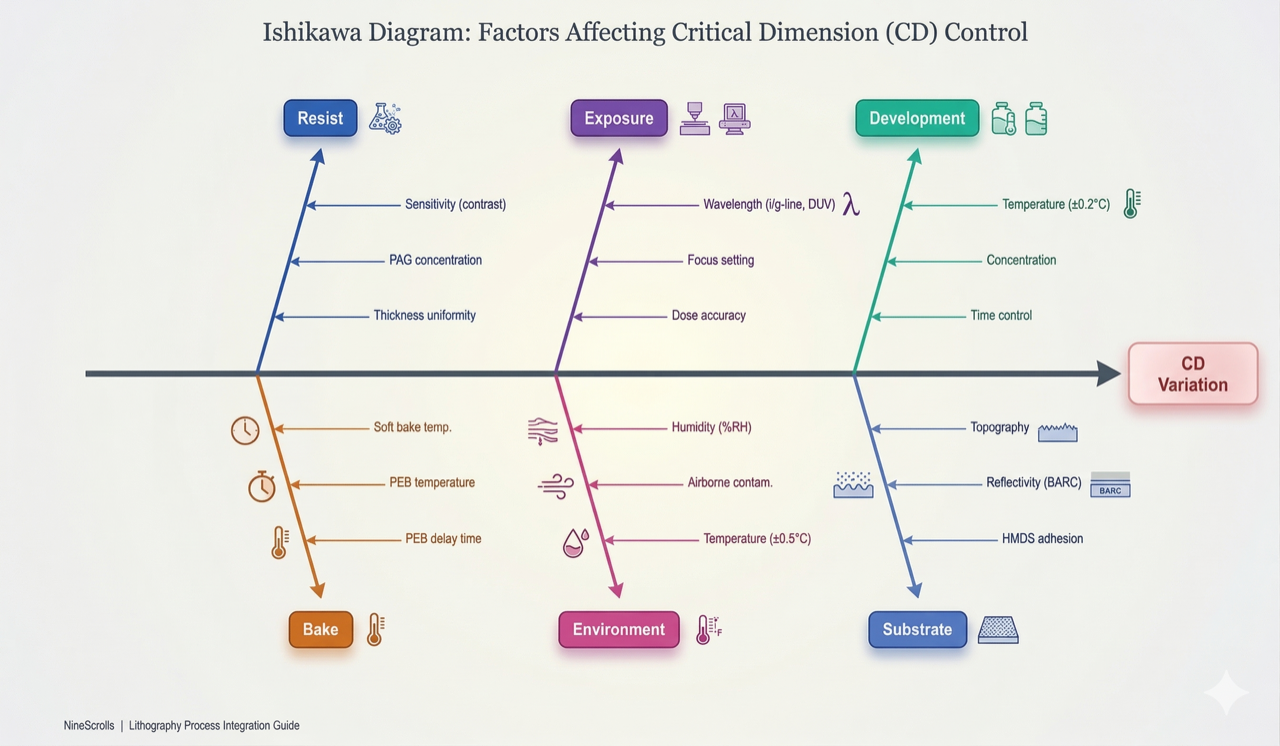

- CD control across the flow depends on resist thickness uniformity (±1%), exposure dose control (±2%), PEB temperature uniformity (±0.5°C), and development time precision (±1 s) — these four factors account for >80% of CD variation.

- Overlay accuracy is determined by mask/reticle quality, alignment system capability, and substrate flatness — achieving <0.5 µm overlay requires careful attention to all three.

- Process integration failures (lifting, scumming, CD drift, etch undercut) are almost always traceable to a specific step interface — use the troubleshooting table in Section 10 for systematic diagnosis.

1) Why Process Integration Matters

Individual lithography steps — coating, exposure, development, etching — are well-understood in isolation. The real challenge lies in integration: ensuring that each step's output meets the next step's input requirements across the entire wafer, lot after lot. A perfectly optimized spin coat is worthless if the soft bake drives off too much solvent for the chosen exposure dose, or if the develop process creates residue that blocks subsequent etch pattern transfer.

Figure 1: Complete lithography process flow — eight integrated steps from substrate preparation through pattern transfer, with corresponding wafer cross-sections showing the state of resist, oxide, and substrate layers at each stage

Process integration engineers think in terms of transfer functions: how does a change in parameter X at step N propagate to the final CD, profile, and defect density after step N+5? This systems-level perspective distinguishes integration engineering from single-step process development.

This guide walks through the complete lithography-to-etch integration flow, emphasizing the critical interfaces between steps and providing practical guidance for building robust, manufacturable patterning processes.

2) Step 1 — Substrate Cleaning

Every lithography flow begins with a clean substrate. Surface contamination — organic films, particles, native oxide, adsorbed moisture — directly impacts resist adhesion, coating uniformity, and pattern fidelity. The cleaning strategy depends on the substrate material and the contamination type.

2.1 Common Cleaning Methods

| Method | Target Contaminants | Typical Substrates | Key Parameters |

|---|---|---|---|

| Piranha (H&sub2;SO&sub4;/H&sub2;O&sub2;) | Organic residues, photoresist | Si, SiO&sub2;, glass | 3:1 ratio, 120°C, 10–15 min |

| RCA SC-1 (NH&sub4;OH/H&sub2;O&sub2;/H&sub2;O) | Particles, organic films | Si, SiO&sub2; | 1:1:5 ratio, 70–80°C, 10 min |

| RCA SC-2 (HCl/H&sub2;O&sub2;/H&sub2;O) | Metal ions (Na, Fe, Cu) | Si, SiO&sub2; | 1:1:6 ratio, 70–80°C, 10 min |

| O&sub2; Plasma | Organic films, surface activation | All (non-oxidizable metals need H&sub2;/N&sub2;) | 200–400 W, 200–500 mTorr, 30–60 s |

| Solvent Clean (acetone/IPA) | Organic residues, grease | All substrates | Sequential rinse, N&sub2; blow-dry |

| UV-Ozone | Thin organic films, surface activation | All substrates | 5–20 min exposure, 185/254 nm UV |

2.2 Critical Interface: Cleaning → HMDS Priming

The time between cleaning and HMDS priming is the first critical process interface. After cleaning, the substrate surface is hydrophilic (high surface energy, water contact angle <10°), which is ideal for HMDS reaction. However, this surface re-contaminates rapidly:

- Airborne organics adsorb within minutes, reducing surface energy and degrading HMDS coverage

- Moisture re-adsorption occurs in seconds in ambient cleanroom air (∼40% RH), forming a water monolayer that must be driven off before HMDS priming

- Native oxide regrowth on Si surfaces begins immediately after HF-last cleans, changing the surface chemistry for HMDS bonding

Best practice: Move substrates from cleaning to HMDS priming within 30 minutes. If delay is unavoidable, store wafers in a dry N&sub2; cabinet or apply a dehydration bake (150–200°C, 5 min) immediately before priming.

3) Step 2 — HMDS Priming

Hexamethyldisilazane (HMDS) is an adhesion promoter that converts the hydrophilic substrate surface (Si–OH) to a hydrophobic one (Si–O–Si(CH&sub3;)&sub3;) by replacing surface hydroxyl groups with trimethylsilyl groups. This hydrophobic surface forms strong bonds with the organic photoresist, preventing resist delamination during development and etching.

3.1 HMDS Application Methods

| Method | Coverage Quality | Throughput | Best For |

|---|---|---|---|

| Vapor prime (oven) | Excellent — monolayer coverage, uniform | 25–50 wafers/batch, 20–30 min cycle | Production, critical layers |

| Spin-on HMDS | Good — may have edge non-uniformity | Single wafer, 30–60 s | R&D, small batch, integrated tracks |

| Vapor prime (inline) | Excellent — integrated with coat track | Continuous, matched to coater speed | High-volume manufacturing |

3.2 HMDS Process Parameters

For vapor-phase HMDS priming, the critical parameters are:

- Dehydration bake: 150–200°C for 60–120 s to drive off adsorbed water. This step is essential — HMDS reacts with water rather than surface hydroxyls if moisture is present, consuming the reagent without promoting adhesion.

- HMDS vapor exposure: 60–120 s at 100–150°C in a closed oven. The wafer temperature must be below the HMDS decomposition point (~250°C).

- Purge: N&sub2; purge to remove unreacted HMDS and reaction byproducts (NH&sub3;). Residual NH&sub3; can contaminate chemically amplified resists, causing T-topping defects.

Verification: A properly HMDS-primed surface exhibits a water contact angle of 65–75°. If the contact angle is below 50°, adhesion failures during development are likely.

3.3 Critical Interface: HMDS → Spin Coating

HMDS-primed surfaces are stable for several hours in a cleanroom environment, but best practice is to coat within 2 hours. Prolonged delays allow airborne contamination to degrade the HMDS monolayer. For chemically amplified resists, the interval must be tightly controlled because residual amine contamination from the HMDS priming environment can poison the photoacid generator (PAG) at the resist surface.

4) Step 3 — Spin Coating

Spin coating applies a uniform layer of photoresist to the primed substrate. The process physics and parameter optimization are covered in detail in our Spin Coating & Development Guide. Here we focus on the integration aspects that connect spin coating to adjacent process steps.

4.1 Integration-Critical Coating Parameters

- Film thickness target: Determined by the downstream etch requirement. The resist must survive the full etch process with margin — a common rule is resist:etch selectivity × etch depth × 1.3 = minimum resist thickness. For example, etching 500 nm of SiO&sub2; with 3:1 selectivity requires ≥215 nm of resist.

- Thickness uniformity: ±1% (1σ) across the wafer is the target for critical layers. Thickness variation directly translates to CD variation through the exposure dose-to-clear relationship — a 2% thickness variation causes approximately 2–4% CD variation depending on resist contrast.

- Edge bead: The thickened resist at the wafer edge (typically 2–5 mm wide, 2–3× nominal thickness) can cause contact/proximity lithography issues by preventing uniform mask-wafer gap. Edge bead removal (EBR) with solvent dispense during spin is standard practice.

4.2 Critical Interface: Spin Coating → Soft Bake

The time between coating and soft bake (the "queue time") affects resist performance. Freshly coated resist contains 20–30% residual solvent. As solvent evaporates in ambient conditions, the film densifies unevenly (edges first, center last), leading to thickness non-uniformity and altered dissolution behavior during development.

Best practice: Begin soft bake within 5 minutes of coating. In automated track systems, the coat-to-bake transfer is immediate (seconds). In manual processing, keep queue times consistent across all wafers in a lot to avoid wafer-to-wafer CD variation.

5) Step 4 — Soft Bake (Pre-Bake)

Soft bake removes most of the residual solvent from the coated resist film, converting it from a viscous liquid to a solid film suitable for exposure. The bake also relieves coating-induced stress and improves resist adhesion to the substrate.

5.1 Soft Bake Parameters

| Parameter | Typical Range | Effect of Increase | Effect of Decrease |

|---|---|---|---|

| Temperature | 90–120°C (resist-dependent) | More solvent removed; higher exposure dose required; improved adhesion | More residual solvent; lower exposure dose needed; risk of incomplete bake |

| Time | 60–120 s (hotplate) | Diminishing returns after solvent is fully driven off; no benefit beyond plateau | Residual solvent causes sticking to mask, poor development, bubble formation |

| Method | Hotplate (preferred) or convection oven | Hotplate: bottom-up baking, skin-free surface. Oven: uniform but slow, can form solvent-trapping skin | — |

Hotplate baking is strongly preferred over convection ovens for critical lithography. In convection ovens, the resist surface heats first and forms a skin that traps solvent beneath, leading to bubbles during exposure and development. Hotplate baking heats from the substrate up, allowing solvent to escape freely from the resist surface.

5.2 Residual Solvent Content

After optimal soft bake, the resist retains 3–8% residual solvent (by weight). This residual solvent is important — it acts as a plasticizer that maintains the resist's photosensitivity. Over-baking drives off too much solvent, reducing dissolution rate contrast and increasing the required exposure dose. Under-baking leaves too much solvent, causing mask sticking in contact lithography and poor development control.

5.3 Critical Interface: Soft Bake → Exposure

After soft bake, the coated wafer must be at a stable, uniform temperature before exposure. If the wafer is still warm when placed on the aligner/stepper chuck, thermal expansion causes overlay errors. Most lithography tracks include a post-bake chill step (chuck at 23°C, 30–60 s) to bring the wafer to a defined temperature before alignment.

For chemically amplified resists, the delay between soft bake and exposure is critical. The photoacid generator (PAG) at the resist surface can be neutralized by airborne amines (parts-per-billion levels of NH&sub3; or NMP vapor). This causes a thin "dead zone" at the resist surface that manifests as T-topping (mushroom-shaped profiles) after development. Chemical filtration of the lithography bay atmosphere is essential for DUV processing.

6) Step 5 — Alignment & Exposure

Exposure transfers the mask pattern into the photoresist by selectively altering the resist's solubility in developer. The choice of exposure mode determines resolution, throughput, overlay accuracy, and equipment complexity.

6.1 Exposure Mode Comparison

| Mode | Resolution | Throughput | Overlay | Mask Type | Best For |

|---|---|---|---|---|---|

| Contact | ∼0.5–1 µm | High (full wafer/shot) | ±0.5–1 µm | 1:1 photomask | R&D, MEMS, PCB |

| Proximity | ∼2–5 µm | High | ±1–2 µm | 1:1 photomask | Large features, mask preservation |

| Projection (stepper) | ∼0.25–1 µm (i-line/DUV) | Medium (step & repeat) | ±50–250 nm | 4×/5× reticle | IC fabrication, advanced MEMS |

| Direct-write (e-beam) | <10 nm | Low (serial write) | ±10–50 nm | Maskless | Prototyping, mask-making, nano R&D |

| Direct-write (laser) | ∼0.5–2 µm | Low–Medium | ±0.25–1 µm | Maskless | Prototyping, small batch |

6.2 Exposure Dose and CD Control

The exposure dose (energy per unit area, mJ/cm²) must be matched to the resist's sensitivity and the target feature size. The relationship between dose and developed linewidth is governed by the resist's contrast curve:

- Under-exposure: Insufficient dose leaves partially exposed resist that develops slowly, producing wider features (for positive resist) or narrower features (for negative resist)

- Over-exposure: Excess dose exposes resist beyond the intended pattern boundaries, producing narrower features (positive) or wider features (negative)

- Dose-to-size: The dose at which the developed feature width matches the mask feature width. This is the target operating point, and it shifts with resist thickness, soft bake conditions, and development parameters.

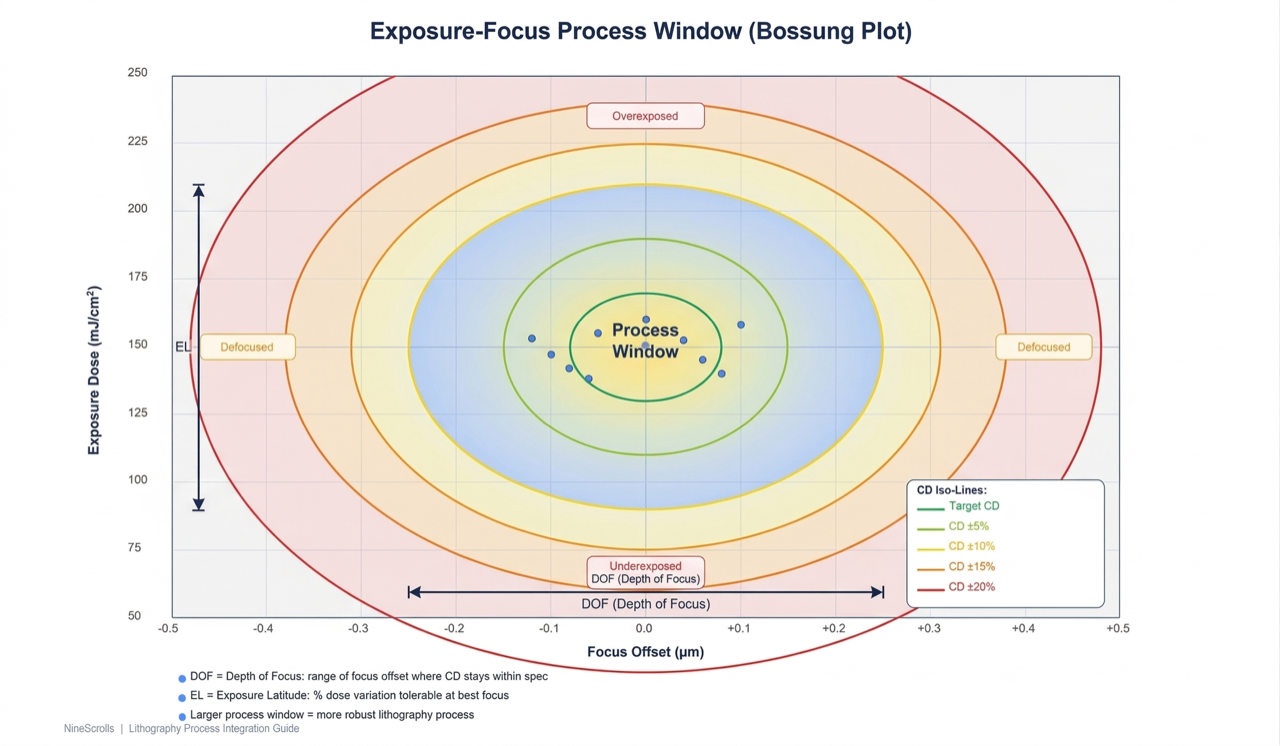

For critical CD control, the exposure dose window must be characterized experimentally using a focus-exposure matrix (FEM): expose a wafer with systematically varied dose and focus settings, develop, and measure CDs. The FEM reveals the process window — the range of dose and focus that produces CDs within specification. A robust process has a wide process window; a fragile process has a narrow one.

6.3 Alignment and Overlay

For multi-level patterning, each layer must be precisely aligned to the previous one. Overlay error has multiple contributors:

- Alignment mark quality: Previous-level alignment marks must be clearly visible through the resist. Topography, thin-film interference, and resist thickness variation affect mark contrast.

- Mechanical accuracy: The aligner/stepper's stage positioning accuracy (interferometer-controlled in steppers, microscope-aided in contact aligners).

- Wafer distortion: Film stress, thermal effects, and prior process steps can cause wafer bow and local distortion that cannot be corrected by rigid-body alignment alone.

- Mask/reticle accuracy: Pattern placement error on the mask translates directly to overlay error on the wafer (1:1 for contact/proximity; reduced by lens magnification for projection).

7) Steps 6–7 — Post-Exposure Bake & Development

7.1 Post-Exposure Bake (PEB)

For chemically amplified (CA) resists — the dominant resist platform for DUV (248/193 nm) and most modern i-line applications — PEB is where the actual chemistry happens. During exposure, photoacid generators produce a catalytic amount of acid. During PEB, this acid catalyzes deprotection reactions that change the resist's solubility. PEB temperature and uniformity are the most critical parameters for CD control:

- PEB temperature sensitivity: 1°C change in PEB temperature causes 5–15 nm CD change for typical CA resists. This demands hotplate temperature uniformity of ±0.3°C across the wafer.

- PEB time: Typically 60–90 s. The reaction is diffusion-limited, so longer PEB increases acid diffusion length and blurs the latent image. Too short PEB leaves incomplete deprotection.

- PEB delay sensitivity: For CA resists, the delay between exposure and PEB must be minimized and kept consistent. During delay, the photoacid can diffuse, neutralize (by airborne amines), or decompose, causing CD drift. In production, the exposure-to-PEB delay is typically <60 s.

For classical DNQ/novolac resists (e.g., AZ 1500 series), PEB is optional — the exposure directly changes the resist's dissolution rate. However, a brief PEB (100–110°C, 60 s) can improve contrast by completing the indene carboxylic acid reaction.

7.2 Development

Development converts the latent image into a physical relief pattern by selectively dissolving the exposed (positive resist) or unexposed (negative resist) regions. Development method, time, and chemistry directly impact CD, line-edge roughness (LER), and defect density. For detailed coverage of development optimization, see our Spin Coating & Development Guide.

7.3 Integration-Critical Development Parameters

| Parameter | Typical Value | Impact on CD | Impact on Downstream Etch |

|---|---|---|---|

| Developer concentration | 2.38% TMAH (standard) | Higher conc. = faster dissolution = wider openings (positive) | Over-development thins resist, reducing etch budget |

| Development time | 30–90 s (puddle), 15–45 s (spray) | ±5 s variation → ±20–50 nm CD change | Under-development leaves scum that blocks etch |

| Development method | Puddle or spray | Puddle: better uniformity; Spray: faster, more aggressive | Spray can cause resist erosion on small features |

| Rinse | DI water, 15–30 s | Stops dissolution; inadequate rinse causes CD drift | Developer residue causes localized etch rate variation |

7.4 Post-Develop Inspection

After development, inspect the wafer before proceeding to hard bake or etch. Key checks:

- CD measurement: Optical CD (OCD) or SEM measurement at multiple sites across the wafer to verify uniformity

- Resist profile: Cross-section SEM (if available) to verify sidewall angle (>85° for anisotropic etch, undercut acceptable for lift-off)

- Scum check: Optical microscopy or AFM to verify complete clearing in developed regions. If scum is present, a brief O&sub2; plasma descum (100–200 W, 10–20 s) resolves it without significantly eroding the resist pattern

- Overlay measurement: For multi-level processes, verify overlay accuracy using dedicated alignment verniers or box-in-box targets

8) Step 8 — Hard Bake

Hard bake (post-develop bake) further densifies the developed resist pattern by driving off remaining solvent and increasing the resist's thermal and chemical stability for the subsequent etch step. Hard bake is not always required — many modern processes skip it when the soft-baked resist provides sufficient etch resistance — but it is essential when:

Figure 3: Exposure-focus process window (Bossung plot) — the central elliptical region defines the acceptable range of dose and focus combinations that maintain CD within specification; DOF and exposure latitude determine manufacturing robustness

- The etch process involves significant substrate heating (>100°C)

- Long etch times (>5 min) require maximum resist durability

- The resist must withstand aggressive etch chemistries (e.g., Cl&sub2;-based metal etching)

- Wet etch processes with strong acids or solvents are used for pattern transfer

8.1 Hard Bake Parameters and Tradeoffs

| Temperature Range | Effect on Resist | Impact on Profile | Downstream Consideration |

|---|---|---|---|

| 110–120°C | Moderate densification; residual solvent removal | Minimal profile change; slight corner rounding | Easy resist strip; compatible with all stripping methods |

| 120–140°C | Significant densification; improved etch resistance | Measurable resist flow; ∼5–10° sidewall angle change | Slightly harder strip; O&sub2; plasma strips effectively |

| >150°C | Cross-linking begins; resist becomes thermally stable | Significant resist flow and rounding; feature broadening | Resist harder to strip; may need high-power O&sub2;/CF&sub4; or elevated temperature |

Key tradeoff: Higher hard bake temperature improves etch resistance but degrades resist profile through thermal flow. For sub-micron features, hard bake temperature must remain below the resist's glass transition temperature (Tg) to prevent feature rounding. Most novolac resists have Tg of 120–140°C; chemically amplified resists vary widely (90–200°C depending on formulation).

8.2 Critical Interface: Hard Bake → Etch

After hard bake, the resist pattern is ready for etch pattern transfer. The interface considerations are:

- Resist budget: The remaining resist thickness after hard bake (accounting for soft bake and develop thinning) must exceed the required etch depth divided by the resist-to-substrate selectivity, with adequate margin (≥30% recommended).

- Resist profile: If the hard bake caused resist flow, the sidewall angle at the top of the resist feature may be rounded, potentially broadening the transferred pattern during etch.

- Surface condition: The resist surface should be free of particles and moisture. A brief N&sub2; blow or vacuum desorption in the etch chamber load-lock serves this purpose.

- Queue time: The delay between hard bake and etch is less critical than earlier queue times (the resist is now stable), but extended delays (>24 hours) can allow moisture absorption that affects etch selectivity.

9) Step 9 — Pattern Transfer (Etch)

Pattern transfer converts the resist relief image into a permanent pattern in the underlying substrate or thin film. The choice of etch method depends on the material being etched, the required profile, and the feature dimensions.

9.1 Etch Method Selection

| Etch Method | Profile | Min Feature Size | Selectivity | Typical Application |

|---|---|---|---|---|

| Wet etch (isotropic) | Undercut = etch depth | >5 µm (with undercut) | Very high (10:1 to >100:1) | Blanket etch, large features, MEMS release |

| RIE | Anisotropic (80–89°) | ∼0.5 µm | Moderate (3:1 to 10:1) | Dielectric etch, shallow pattern transfer |

| ICP-RIE | Highly anisotropic (>89°) | <100 nm | High (5:1 to 50:1) | Deep Si etch, advanced patterning, photonics |

| DRIE (Bosch/Cryo) | Vertical (∼90°) | ∼1 µm (AR-dependent) | Very high (>50:1 to resist) | MEMS, TSV, high-aspect-ratio structures |

For comprehensive coverage of RIE/ICP-RIE process optimization, see our Reactive Ion Etching Guide.

9.2 Etch Integration Considerations

- Resist erosion during etch: Monitor resist thickness in-situ (laser reflectometry) or ex-situ (profilometry) to ensure the resist mask survives the entire etch. If resist budget is marginal, reduce RF bias power, add passivation gas (e.g., CHF&sub3; for oxide etch), or use a hard mask.

- CD transfer bias: The final etched CD is typically 20–100 nm different from the developed resist CD due to resist erosion, faceting, and lateral etch. This "etch bias" must be characterized and compensated in the mask design (optical proximity correction, OPC) or the lithography step (intentional dose offset).

- Loading effects: Etch rate varies with the fraction of exposed area (macro-loading) and the local pattern density (micro-loading). Dense arrays etch more slowly than isolated features because etchant species are consumed faster in densely patterned regions.

- Endpoint detection: Use optical emission spectroscopy (OES), laser interferometry, or mass spectrometry to detect when the target film has been completely etched. Over-etching into the underlying layer causes damage; under-etching leaves residual material that becomes a defect.

- Etch-induced damage: Energetic ion bombardment during RIE/ICP-RIE can damage the substrate surface to a depth of 2–20 nm. For gate oxide and III-V devices, post-etch annealing or surface treatment may be needed to recover electrical performance.

10) Step 10 — Resist Strip

After pattern transfer, the resist mask must be completely removed without damaging the underlying patterned structure. Resist strip is often the most challenging integration step because the resist has been modified by etch exposure — UV hardening, ion implantation (if used), and polymer cross-linking make post-etch resist significantly harder to remove than virgin resist.

For detailed coverage of plasma stripping chemistries and optimization, see our Plasma Stripping & Ashing Guide.

10.1 Resist Strip Method Selection

| Strip Method | Mechanism | Resist Type | Substrate Compatibility |

|---|---|---|---|

| O&sub2; plasma (direct) | Radical oxidation + ion-assisted | Standard & hardened PR | Si, SiO&sub2;, SiN (not Cu/metal-sensitive) |

| O&sub2; plasma (downstream) | Radical oxidation only | Standard PR | Damage-sensitive substrates, III-V |

| H&sub2;/N&sub2; plasma | Reductive stripping | Standard & hardened PR | Cu, low-k, metal interconnects |

| Wet solvent (NMP, DMSO) | Chemical dissolution | Standard PR, lift-off resists | All substrates (solvent-compatible) |

| Piranha (H&sub2;SO&sub4;/H&sub2;O&sub2;) | Oxidative dissolution | All organic resists | Si, SiO&sub2; (not metals, not III-V) |

11) CD Control Through the Full Flow

Achieving tight CD control (±5% of target) across the entire lithography-etch flow requires understanding how each step contributes to the final CD variation budget. The table below shows typical contributions:

Figure 2: Ishikawa (fishbone) diagram of CD variation sources — six major categories (resist, exposure, development, bake, environment, substrate) each contribute multiple sub-factors that must be controlled for tight CD uniformity

| Process Step | CD Variation Contributor | Typical Magnitude (3σ) | Control Strategy |

|---|---|---|---|

| Spin coating | Thickness variation → dose-to-clear shift | ±5–15 nm | Coat uniformity ±1%; dispense volume control |

| Soft bake | Residual solvent variation → sensitivity change | ±3–10 nm | Hotplate uniformity ±0.5°C; consistent queue time |

| Exposure | Dose non-uniformity, focus error, diffraction | ±10–30 nm | Dose control ±2%; focus ±0.1 µm; FEM characterization |

| PEB | Temperature-driven acid diffusion variation | ±5–20 nm (CA resists) | PEB uniformity ±0.3°C; consistent PEB delay |

| Development | Dissolution rate non-uniformity | ±5–15 nm | Timed puddle develop; fresh developer; uniform dispense |

| Etch | Etch rate non-uniformity, resist erosion, loading | ±10–30 nm | Endpoint detection; optimized gas distribution; load compensation |

The total CD variation is the root-sum-square (RSS) of individual contributions. For a typical i-line process targeting 1 µm features, total 3σ CD variation of ±30–50 nm is achievable with well-controlled equipment and processes.

12) Common Process Integration Challenges

12.1 Troubleshooting Guide

| Symptom | Most Likely Step | Root Cause | Corrective Action |

|---|---|---|---|

| Resist lifting during development | HMDS / cleaning | Poor adhesion from inadequate priming or contaminated substrate | Verify HMDS contact angle (>65°); re-clean substrate; reduce clean-to-HMDS delay |

| Scum in open areas after develop | Development / exposure | Under-exposure or under-development; weak developer | Increase dose; extend develop time; O&sub2; descum (100 W, 15 s) |

| T-topping (mushroom profiles) | PEB delay / environment | Airborne amine contamination neutralizing surface acid (CA resists) | Minimize exposure-to-PEB delay; install chemical filters; verify HVAC |

| CD drift wafer-to-wafer | Queue times / bake | Inconsistent coat-to-bake or exposure-to-PEB delays | Standardize queue times; use automated track; monitor lot timing |

| Etch undercut beneath resist | Hard bake / etch | Insufficient hard bake allowing resist edge lift; isotropic etch component too high | Increase hard bake temp; reduce etch pressure; increase bias for directionality |

| Resist burning/bubbles during etch | Soft bake / etch | Excessive residual solvent trapped in resist; etch power too high | Extend soft bake; add hard bake step; reduce etch power/add cooling |

| Resist mask eroded before etch complete | Resist thickness / etch | Insufficient resist budget; poor selectivity; resist not hard-baked | Increase resist thickness; optimize etch selectivity; hard bake at 120–130°C; consider hard mask |

| Overlay errors > spec | Alignment / substrate | Poor alignment mark contrast; wafer distortion; thermal drift | Re-optimize alignment recipe; check wafer flatness; stabilize wafer temperature before alignment |

Related Articles

- Spin Coating & Development Guide — detailed coverage of coat and develop process optimization

- Reactive Ion Etching (RIE) Guide — comprehensive RIE/ICP-RIE process reference

- Plasma Stripping & Ashing Guide — post-etch resist removal strategies

- Post-Etch Cleaning & Residue Removal — damage-free residue removal after pattern transfer

13) Frequently Asked Questions

What is the most common cause of lithography process integration failure?

Inconsistent queue times between process steps. Unlike individual step parameters that are machine-controlled and reproducible, queue times depend on operator scheduling, equipment availability, and lot flow. A 30-minute delay between coating and soft bake that varies by ±15 minutes across wafers causes 3–5% resist thickness non-uniformity, which propagates to ±10–20 nm CD variation. Similarly, variable PEB delay for chemically amplified resists causes CD drift of 5–15 nm per minute of delay variation. The fix is to standardize queue times (using automated tracks for high-volume processes) and monitor timing as a process parameter, not just as a scheduling convenience.

When should I use a hard mask instead of photoresist for pattern transfer?

Use a hard mask when: (1) the etch depth exceeds the resist budget — for example, etching >2 µm of Si with a resist that gives only 3:1 selectivity would require >700 nm of resist, which may exceed the maximum thickness compatible with your resolution target; (2) the etch chemistry is incompatible with organic resist — chlorine-based metal etching at elevated temperatures rapidly erodes organic masks; (3) you need extremely precise CD control, since hard masks (SiO&sub2;, SiN, Cr, Al&sub2;O&sub3;) do not exhibit thermal flow or lateral erosion during etch. Common hard mask materials include PECVD SiO&sub2; (for Si etch with fluorine chemistry), SiN (for oxide etch), and sputtered Cr or Al (for various substrates). The tradeoff is additional deposition, patterning, and removal steps.

How do I determine the correct exposure dose for a new resist-substrate combination?

Run a dose matrix (also called exposure latitude test): coat a wafer, expose different fields across the wafer at systematically varied doses (e.g., 50–200 mJ/cm² in 10% increments for a typical i-line resist), develop with standard parameters, and measure the resulting CDs or clearing behavior. For an initial estimate, start with the resist manufacturer's recommended dose and bracket ±50%. Plot CD vs. dose to identify the dose-to-size (where developed CD matches the mask CD). Then run a full focus-exposure matrix (FEM) at the identified dose range to map the process window. The optimal operating point is the center of the largest rectangular area on the FEM that keeps CDs within specification — this provides maximum tolerance to dose and focus variations in production.

Can I skip HMDS priming for negative photoresists?

It depends on the resist and substrate. Many negative resists (e.g., SU-8, ma-N series) have built-in adhesion promoters and adhere well to clean SiO&sub2; and Si substrates without HMDS. However, HMDS priming is still recommended when: (1) working with substrates that have poor natural adhesion to organics (metals, III-V compounds, polymers), (2) patterning very small features (<2 µm) where even slight adhesion weakness causes liftoff during development, or (3) using aggressive development conditions (long develop times, high developer concentration) that stress the resist-substrate interface. When in doubt, run a split experiment: coat with and without HMDS, develop, and inspect for lifting or delamination at feature edges.

What overlay accuracy can I achieve with a manual contact aligner vs. a stepper?

Manual contact aligners typically achieve ±0.5–2 µm overlay accuracy, depending on the operator's skill, alignment mark design, and microscope quality. Semi-automated aligners with motorized stages and split-field optics can reach ±0.25–0.5 µm. Steppers with interferometer-controlled stages routinely achieve ±50–250 nm (machine-to-machine varies). For perspective: if your minimum feature size is 2 µm, a manual aligner with ±1 µm overlay is adequate. If your features are below 1 µm, a stepper is necessary. The key is that overlay budget should be ≤1/3 of the minimum feature size to avoid electrical shorts or opens at layer interfaces.

NineScrolls Lithography & Pattern Transfer Equipment

From spin coating to pattern transfer and resist strip, NineScrolls provides the complete equipment chain for lithography process integration. Our coater/developer systems deliver ±1% thickness uniformity, RIE and ICP etchers provide precise pattern transfer with endpoint detection, and Striper systems handle post-etch resist removal — all engineered for tight process control and integration flexibility.