Quantum Device Micro‑ & Nanofabrication – Processes, Challenges, and Equipment Guide

By NineScrolls Engineering · 2026-04-04 · 20 min read · Nanotechnology

Target Readers: Quantum hardware engineers, process engineers, PIs and lab managers building quantum device fabrication capabilities, R&D procurement teams evaluating nanofabrication equipment for quantum applications. Researchers transitioning from conventional CMOS or MEMS fabrication to quantum device processing will find the platform-specific sections and cross-contamination guidelines especially relevant.

TL;DR Summary

Quantum devices — superconducting qubits, semiconductor spin qubits, photonic quantum circuits, and topological structures — demand fabrication tolerances far beyond conventional microelectronics. Material purity (especially for superconductors like Nb and Al), interface quality, and process-induced defect control directly determine qubit coherence times and gate fidelities. This guide walks through the complete fabrication chain: substrate preparation, thin-film deposition (sputtering, e-beam evaporation, ALD, PECVD), lithography (EBL, photolithography, direct-write), pattern transfer (RIE, ICP-RIE, IBE), lift-off and Josephson junction formation, packaging, and yield management — with practical process windows and equipment selection criteria for each step.

1) Why Quantum Devices Need Special Fabrication

In classical CMOS, a transistor either switches or it doesn't — fabrication defects reduce yield but don't fundamentally alter device physics. Quantum devices are different. A single two-level system (TLS) defect at a metal–substrate interface can limit qubit T₁ relaxation time from milliseconds to microseconds. Surface oxide quality, grain boundary density in superconducting films, and even residual photoresist at the atomic monolayer level directly determine whether a quantum processor achieves error-correction thresholds.

Key Fabrication Challenges

| Challenge | Classical IC Impact | Quantum Device Impact |

|---|---|---|

| Interface defects (TLS) | Minor leakage | Dominant T₁ loss channel; limits coherence |

| Surface oxide | Contact resistance | Parasitic capacitance, dielectric loss (tan δ) |

| Film stress | Wafer bow | Shifts qubit frequency, Josephson junction Ic |

| Etch residue | Yield loss | TLS formation, spurious coupling |

| Cross-contamination | Threshold shift | Quasiparticle poisoning (kills coherence) |

| Dimensional variation | Speed binning | Frequency collision between qubits |

These constraints make quantum fabrication arguably the most demanding application of micro/nanofabrication today — tighter tolerances than MEMS, cleaner interfaces than photonics, and lower defect densities than any other solid-state platform.

2) Quantum Device Platforms & Their Fabrication Requirements

2.1 Superconducting Qubits (Transmon, Fluxonium, etc.)

Superconducting qubits are the most mature platform, used by IBM, Google, and numerous academic labs. The core structure is deceptively simple: a Josephson junction (Al/AlOₓ/Al tunnel barrier) shunted by a large capacitor, all patterned on a low-loss substrate (typically high-resistivity Si or sapphire).

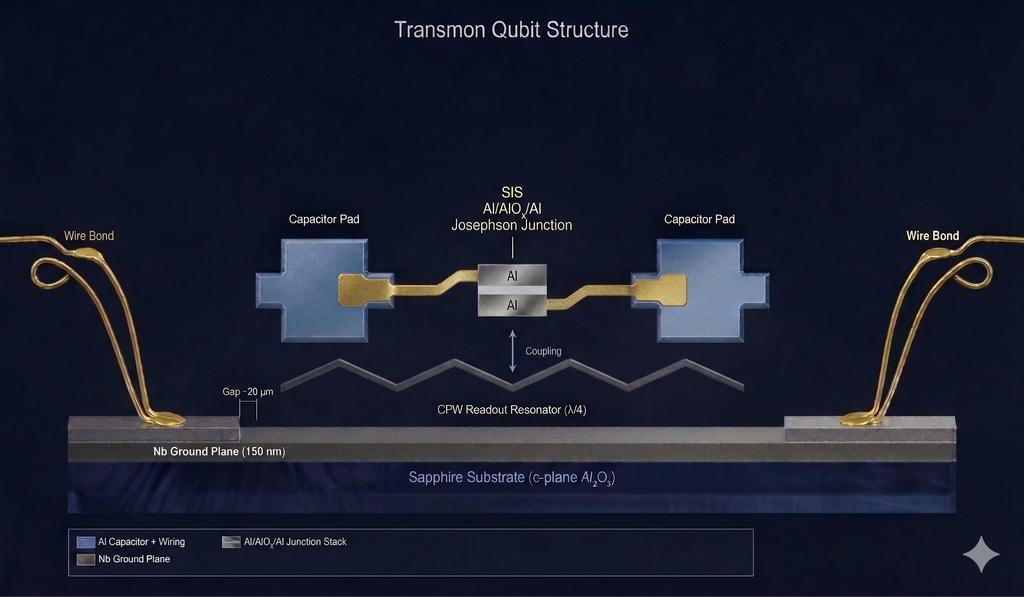

Figure 1: Transmon Qubit Structure — Two Al capacitor pads connected by an Al/AlOₓ/Al Josephson junction on a sapphire substrate, capacitively coupled to a λ/4 CPW readout resonator. The Nb ground plane surrounds the qubit with controlled gap spacing (~20 µm).

Critical fabrication steps:

- Substrate preparation: High-resistivity Si (ρ > 10 kΩ·cm) or c-plane sapphire; piranha + HF dip or buffered oxide etch to remove native oxide; some groups use in-situ Ar plasma clean before deposition

- Ground plane deposition: 100–200 nm Nb or Al via DC magnetron sputtering or e-beam evaporation; Nb requires base pressure < 5 × 10⁻⁸ Torr for low residual resistivity ratio (RRR > 30)

- Ground plane patterning: Photolithography or EBL + RIE/ICP-RIE in SF₆/Ar or Cl₂/BCl₃ chemistry; critical to minimize sidewall damage and re-deposition

- Josephson junction fabrication: Dolan bridge or Manhattan-style double-angle evaporation; EBL on bilayer resist (MMA/PMMA); controlled oxidation (50–200 mTorr O₂, 5–15 min) determines junction Rₙ and Eⱼ

- Airbridges / crossovers: Multi-layer lithography + e-beam evaporation + lift-off; critical for reducing slot-line mode coupling in multi-qubit processors

Process note: The substrate–metal interface contributes > 50% of TLS loss in state-of-the-art transmons. In-situ substrate cleaning immediately before deposition — using Ar/O₂ plasma or ion milling — can improve T₁ by 2–5× compared to ex-situ wet cleaning alone.

2.2 Semiconductor Spin Qubits

Spin qubits encode information in the spin state of individual electrons (or holes) confined in semiconductor quantum dots. The dominant material systems are Si/SiGe heterostructures and GaAs/AlGaAs 2DEGs, with Si/SiGe gaining momentum due to isotopic purification (²⁸Si) enabling T₂* > 100 µs.

Critical fabrication steps:

- Heterostructure growth: MBE-grown Si/SiGe quantum wells with < 0.1% Ge composition variation; this step typically precedes cleanroom processing

- Gate stack definition: 3–5 layers of overlapping metallic gates (Al or Pd), each 20–40 nm wide, patterned by EBL; gate-to-gate alignment < 5 nm required

- Dielectric isolation: ALD Al₂O₃ or HfO₂ (5–10 nm) between gate layers; pinhole-free films essential to prevent gate leakage at mK temperatures

- Ohmic contacts: Selective implantation (P⁺ in Si) + rapid thermal anneal; contact resistance < 1 kΩ at 20 mK

- Mesa isolation: ICP-RIE etch through 2DEG layer; smooth sidewalls to avoid edge-state leakage

2.3 Photonic Quantum Circuits

Integrated photonic quantum circuits manipulate single photons in waveguides, beam splitters, and phase shifters fabricated on silicon nitride (Si₃N₄), silicon-on-insulator (SOI), or lithium niobate (LiNbO₃) platforms. Key requirements are ultra-low optical loss (< 0.1 dB/cm) and precise dimensional control for phase matching.

Critical fabrication steps:

- Waveguide core deposition: PECVD or LPCVD Si₃N₄ (200–800 nm); stress management via multi-step deposition to avoid film cracking; N–H bond absorption at 1520 nm must be minimized by annealing or deuterated precursors

- Waveguide patterning: EBL or DUV stepper lithography + ICP-RIE in CHF₃/O₂ or C₄F₈/SF₆; sidewall roughness < 1 nm RMS required for low scattering loss

- Cladding: PECVD SiO₂ top cladding; refractive index matching critical for symmetric mode confinement

- Single-photon sources: Integration of quantum dots (InAs/GaAs) or color centers (NV in diamond) via transfer printing or heterogeneous bonding

- Detectors: Superconducting nanowire single-photon detectors (SNSPDs) — NbN or WSi films (4–6 nm), patterned by EBL + RIE into 50–100 nm wide nanowires

2.4 Trapped Ion & Neutral Atom Platforms

Surface-electrode ion traps use MEMS-like fabrication to create planar electrode arrays that generate 3D confining potentials for individual ions. While the quantum operations use laser/microwave addressing, the trap chip fabrication involves standard micro/nanofabrication:

- Electrode patterning: Au or Al electrodes (1–5 µm thick) on sapphire or fused silica substrates; electroplating or e-beam evaporation + lift-off

- Dielectric layers: PECVD SiO₂ for inter-layer isolation; low RF loss tangent critical at trap drive frequencies (10–100 MHz)

- Through-substrate vias: DRIE for backside electrical routing; aspect ratios up to 20:1 in Si substrates

- Surface treatment: Ar/O₂ plasma cleaning to reduce anomalous heating from surface contaminants; ion milling for ultra-clean electrode surfaces

3) Core Fabrication Processes for Quantum Devices

3.1 Thin-Film Deposition

Film quality is paramount in quantum device fabrication. Unlike CMOS, where electrical performance is dominated by bulk properties, quantum devices are surface- and interface-limited. The choice of deposition technique and parameters directly impacts defect density, stress, and superconducting properties.

| Technique | Materials | Quantum Application | Key Parameters |

|---|---|---|---|

| DC/RF Magnetron Sputtering | Nb, NbN, NbTiN, TiN, Al | Qubit ground planes, SNSPD films, resonators | Base pressure < 5 × 10⁻⁸ Torr; substrate temp RT–400°C; Ar pressure 2–5 mTorr |

| E-beam Evaporation | Al, Ti, Au, Pd | Josephson junctions (double-angle), gate electrodes | Rate 0.1–1 nm/s; tilt angle ±15–25° for Dolan bridge; in-situ oxidation |

| ALD | Al₂O₃, HfO₂, TiO₂ | Gate dielectrics (spin qubits), tunnel barriers, passivation | Temp 150–300°C; < 0.5% thickness non-uniformity; precursor: TMA/H₂O or TDMAH/H₂O |

| PECVD | SiO₂, Si₃N₄, a-Si | Photonic waveguides, cladding, hard masks | Stress control critical: tensile Si₃N₄ can crack at > 500 nm; H content affects optical loss |

Tip — Nb sputtering for qubits: Target-to-substrate distance, Ar pressure, and DC power together control grain size and RRR (residual resistivity ratio). RRR > 30 correlates with low microwave loss; achieving this typically requires UHV base pressure and < 5 mTorr Ar. Rotating the substrate during deposition improves thickness uniformity to < 2% across 150 mm wafers. See our Magnetron Sputtering Guide for detailed parameter tables.

3.2 Lithography

Quantum devices span a wide range of feature sizes — from millimeter-scale capacitor pads to sub-100 nm Josephson junctions and nanowire detectors. Most quantum fabrication labs use a combination of optical lithography (for larger features) and electron-beam lithography (for critical nanoscale structures).

Electron-Beam Lithography (EBL)

EBL is the workhorse for quantum device nanopatterning. For Josephson junctions, the standard approach uses a bilayer resist stack:

- Bottom layer: MMA(8.5)MAA EL11 or PMGI SF7 — higher sensitivity, creates undercut for clean lift-off

- Top layer: 950K PMMA A4 — high resolution imaging layer

- Exposure: 100 kV acceleration; dose 800–1200 µC/cm² for PMMA; bridge width 80–150 nm for Dolan geometry

- Development: MIBK:IPA 1:3 for PMMA (60–90 s); MF-319 for MMA undercut development

For SNSPD nanowires (50–100 nm), negative-tone resists like HSQ (hydrogen silsesquioxane) or ma-N 2400 are preferred due to their excellent resolution and etch resistance.

Optical Lithography

Contact or projection lithography handles features > 1 µm: capacitor pads, ground planes, coplanar waveguides, alignment marks. i-line (365 nm) steppers with < 0.5 µm overlay accuracy are sufficient for most superconducting qubit layouts. The key consideration is resist residue — any organic contamination at the metal–substrate interface introduces TLS defects, so thorough descum (O₂ plasma, 50–100 W, 30–60 s) after development is critical.

For an overview of lithography process integration including resist selection, bake optimization, and alignment strategies, see our Lithography Process Integration Guide.

3.3 Dry Etching for Quantum Devices

Pattern transfer by dry etching is where many quantum fabrication processes succeed or fail. The critical requirements are:

- Selectivity: Etch the target film without damaging the substrate or underlying layers

- Profile control: Vertical sidewalls for capacitor gaps; smooth sidewalls for waveguides

- Low damage: Minimize ion bombardment damage that creates TLS defects at interfaces

- Clean surface: No fluorocarbon polymer residue or re-deposited material that degrades Q factors

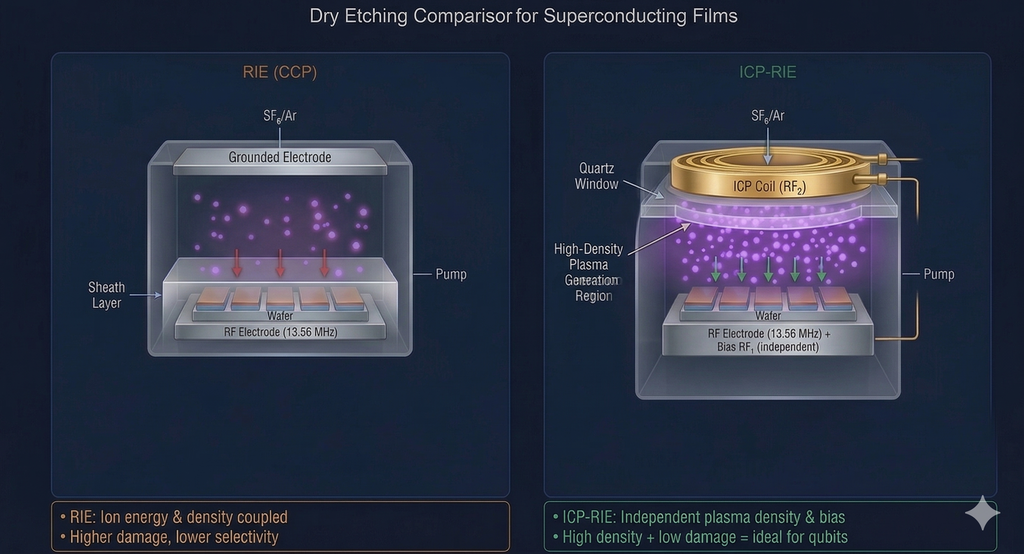

Figure 2: RIE vs ICP-RIE for Superconducting Film Etching — In RIE (left), ion energy and plasma density are coupled via a single RF source, leading to higher damage. In ICP-RIE (right), independent ICP and bias RF sources enable high-density plasma with low ion energy — ideal for minimizing TLS defects in qubit ground planes.

Etching Superconducting Films

| Material | Chemistry | Technique | Notes |

|---|---|---|---|

| Nb | SF₆/Ar or CF₄/O₂ | RIE or ICP-RIE | NbF₅ volatile at RT; add O₂ to improve anisotropy; endpoint by OES (Nb* 405 nm) |

| NbN / NbTiN | SF₆/Ar or Cl₂/BCl₃ | ICP-RIE | Higher ion energy needed than Nb; Cl₂ chemistry gives smoother sidewalls but requires heated chuck |

| Al | Cl₂/BCl₃/Ar | ICP-RIE | Break through native AlOₓ with high-bias strike step; corrosion risk — rinse immediately post-etch |

| TiN | Cl₂/Ar or BCl₃/Cl₂ | ICP-RIE | TiCl₄ volatile; good etch rate at moderate bias; low damage achievable |

| WSi (SNSPD) | SF₆/Ar | RIE | Very thin films (4–6 nm); minimal over-etch critical; endpoint by time with etch-rate calibration |

Etching Photonic Materials

| Material | Chemistry | Technique | Notes |

|---|---|---|---|

| Si₃N₄ | CHF₃/O₂ or C₄F₈/SF₆/Ar | ICP-RIE | Sidewall roughness < 1 nm critical for low loss; optimized C₄F₈/SF₆ ratio controls passivation |

| Si (SOI) | Cl₂/HBr/O₂ or SF₆/C₄F₈ | ICP-RIE | Bosch-like process for deep etch; continuous process for smooth sidewalls in rib waveguides |

| LiNbO₃ | Ar/Cl₂ or Ar (physical) | ICP-RIE or IBE | Low volatility products; redeposition a major issue; IBE preferred for < 3 nm roughness |

Damage mitigation: For superconducting qubit ground planes, reducing ICP-RIE bias power to < 30 W (at the cost of etch rate) can improve internal quality factors Q_i by an order of magnitude. Some groups use a two-step approach: higher bias for bulk etch, then low-bias finishing step for the final 10–20 nm. Post-etch surface treatment (HF dip for Si substrate, or in-situ Ar/H₂ plasma) is recommended. See our RIE Guide and ICP-RIE Guide for process optimization strategies.

3.4 Josephson Junction Fabrication

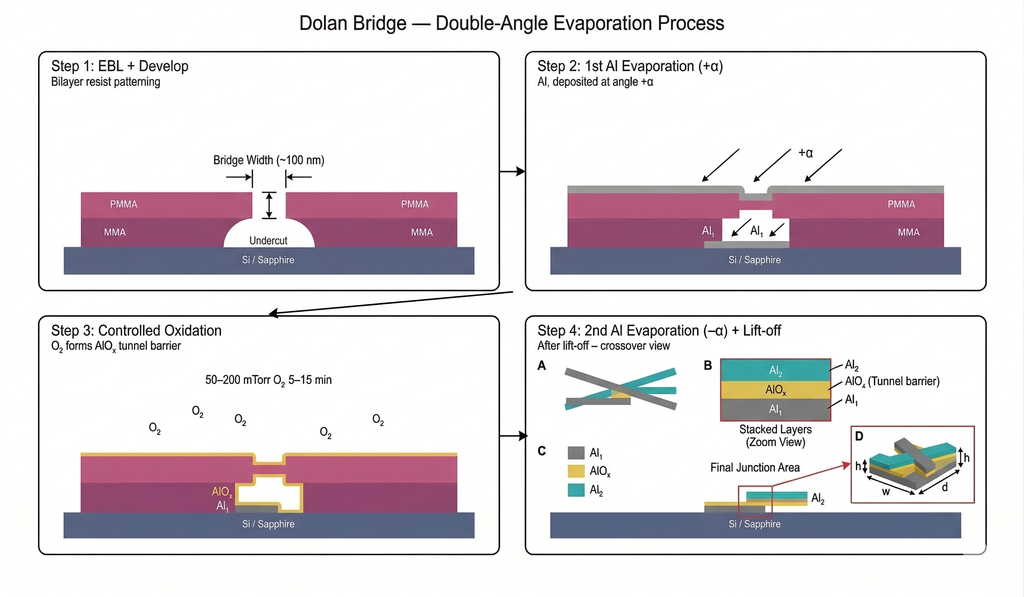

The Josephson junction is the only nonlinear, dissipationless circuit element available — and it's the heart of every superconducting qubit. The most common fabrication approach is the Dolan bridge technique:

Figure 3: Dolan Bridge Process — (Step 1) EBL patterns a ~100 nm bridge in PMMA over MMA undercut. (Step 2) First Al layer evaporated at angle +α. (Step 3) Controlled O₂ exposure forms the AlOₓ tunnel barrier. (Step 4) Second Al layer at −α; the overlap region defines the Josephson junction area.

- Bilayer resist patterning: EBL exposes a narrow bridge in PMMA over a larger undercut in MMA/PMGI

- First Al evaporation: 20–40 nm Al at angle α (typically +20° to +25°) relative to substrate normal

- Controlled oxidation: Static O₂ exposure (50–300 mTorr, 5–30 min) forms the AlOₓ tunnel barrier; junction resistance Rₙ ∝ exp(d/λ), where d is oxide thickness

- Second Al evaporation: 40–80 nm Al at angle −α; the two Al layers overlap only in the junction area

- Lift-off: Warm NMP or acetone soak (2–12 hours) to remove resist and excess metal

Junction parameter control:

| Parameter | Target Range | Controlled By | Sensitivity |

|---|---|---|---|

| Junction area | 0.01–0.1 µm² | EBL dose + bridge width | ±10% area → ±10% Ic |

| Rₙ (normal resistance) | 5–20 kΩ (transmon) | O₂ pressure × time | ±5% Rₙ → ±2.5% Eⱼ |

| Ic (critical current) | 20–50 nA (transmon) | Area × Jc (current density) | Sets qubit frequency; ±50 MHz target |

| Asymmetry (SQUID) | < 5% | EBL alignment + dose uniformity | Affects flux tunability range |

An alternative approach gaining traction is the overlap/bandage junction: separate lithography and deposition steps for each electrode, with an in-situ Ar ion mill to clean the interface before the top electrode. This method offers better process control at scale but requires additional lithography steps.

4) Process Integration & Contamination Control

4.1 Material Compatibility Matrix

Quantum fabrication labs must enforce strict material segregation. The primary concern is cross-contamination between incompatible material systems:

| Contaminant | Source | Impact on Quantum Devices | Mitigation |

|---|---|---|---|

| Au | Previous process in shared chamber | Destroys superconductivity in Al/Nb (even ppm levels) | Dedicated chambers for superconductor processing; no Au in SC qubit fab line |

| Magnetic impurities (Fe, Ni, Co) | Stainless steel tooling, tweezers | Local magnetic fields break Cooper pairs; T₁ killer | Non-magnetic tools; ceramic/PEEK wafer handling |

| Organic residue | Incomplete resist strip, solvent residue | TLS defects at interfaces; dielectric loss | O₂ plasma descum; piranha + solvent rinse; UV/ozone |

| Native oxide regrowth | Air exposure between process steps | Parasitic capacitance, dielectric loss | Minimize queue time; in-situ cleaning before next deposition; N₂ storage |

Lab management note: Many quantum fab groups adopt a "superconductor-clean" policy: dedicated RIE/ICP-RIE chambers, sputtering targets, and resist processing baths that never see Au, Cu, or magnetic materials. This overhead is justified — a single Au-contaminated Nb film wastes weeks of downstream processing. For chamber cleaning and seasoning protocols, see our Chamber Materials & Contamination Control Guide.

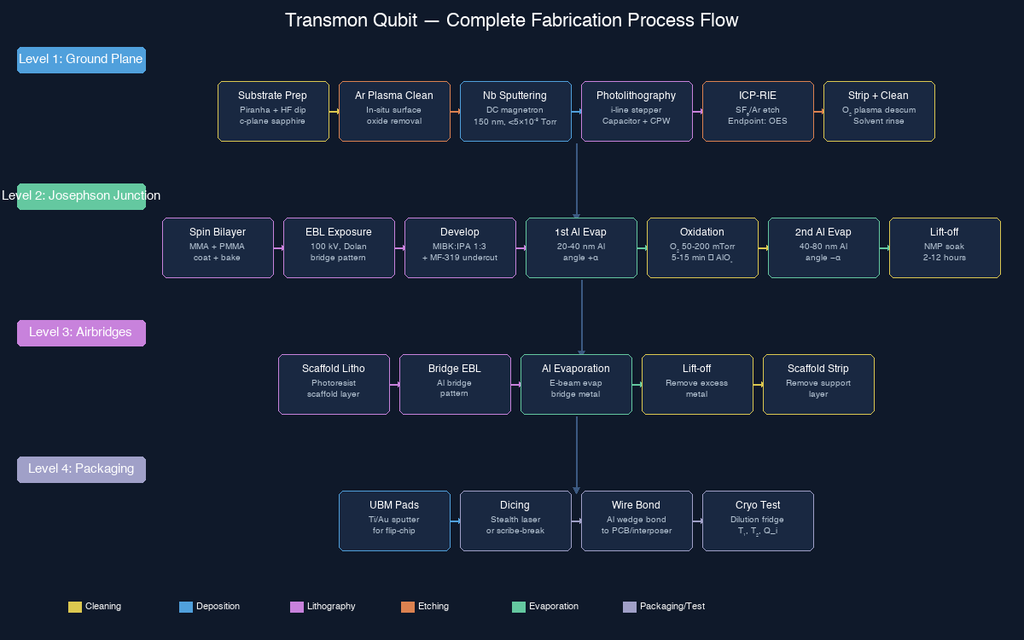

4.2 Process Flow Example: Transmon Qubit

A typical transmon qubit fabrication flow on a 2-inch sapphire substrate involves 4–6 lithography levels:

Figure 4: Transmon Qubit Complete Fabrication Flow — Four process levels from substrate preparation through cryogenic testing. Color coding indicates process category: cleaning (yellow), deposition (blue), lithography (purple), etching (orange), evaporation (green), packaging/test (gray).

- Level 1 — Ground plane: Sputter 150 nm Nb → photolithography → ICP-RIE (SF₆/Ar) → strip resist

- Level 2 — Josephson junctions: Spin bilayer resist → EBL → develop → double-angle Al evaporation with in-situ oxidation → lift-off

- Level 3 — Bandage (optional): EBL → Ar ion mill → Al evaporation → lift-off (strengthens junction contact)

- Level 4 — Airbridges: Photolithography (scaffold) → EBL (bridge) → e-beam evaporate Al → lift-off → scaffold strip

- Level 5 — Under-bump metallization: Photolithography → sputter Ti/Au → lift-off (for flip-chip bonding pads)

- Dicing & packaging: Stealth dicing or scribe-and-break → wire bonding or flip-chip to interposer → install in dilution refrigerator

Total cleanroom time: 5–10 days for experienced operators; 2–4 weeks including characterization feedback loops.

5) Equipment Selection for Quantum Fabrication Labs

5.1 Etching Systems

Quantum device fabrication typically requires both RIE and ICP-RIE capabilities:

- RIE — Suitable for resist descum, simple film patterning (thin Al, dielectrics), and surface cleaning. Lower cost, adequate for features > 500 nm. Look for: low base pressure (< 5 × 10⁻⁶ Torr), precise pressure control (0.1 mTorr resolution), and easy chamber cleaning access.

- ICP-RIE — Essential for Nb/NbN ground planes, photonic waveguides, and any process requiring independent control of ion energy and plasma density. Key specs: separate ICP and bias RF sources, substrate temperature control (−20°C to 200°C), and load-lock to prevent chamber contamination during sample exchange.

- IBE/RIBE — Required for LiNbO₃ photonic circuits, ferroelectric materials, and any material lacking volatile etch products. Also useful for in-situ surface cleaning before deposition (e.g., Ar ion mill before bandage junction). Key specs: beam uniformity < ±3%, tilt/rotation stage for angle-dependent milling.

5.2 Deposition Systems

- Magnetron Sputtering — The primary tool for superconducting films. Requirements for quantum applications: UHV base pressure (< 10⁻⁸ Torr range), confocal target geometry for uniformity, substrate rotation, and gas purity (6N Ar). DC sputtering for metals; RF for dielectrics and compound targets (NbN, TiN).

- PECVD — For dielectric films (SiO₂, Si₃N₄) used in photonic waveguides, inter-layer dielectrics, and hard masks. Low-stress recipes are critical — particularly for Si₃N₄ waveguide cores where tensile stress > 200 MPa can cause cracking. Substrate temperature control and gas ratio precision are key selection criteria.

- ALD — For ultra-thin, conformal dielectric layers. Gate dielectrics in spin qubits (5–10 nm Al₂O₃ or HfO₂) demand < 0.5% thickness uniformity and pinhole-free films. Thermal ALD is preferred over plasma-enhanced ALD for quantum devices to minimize plasma-induced interface damage.

5.3 Ancillary Equipment

- Plasma Cleaners — Low-power O₂/Ar plasma for resist descum, surface activation before bonding, and chamber part cleaning. A benchtop plasma cleaner with controllable power (50–300 W) and selectable gases is invaluable for quick pre-deposition surface treatments.

- Coater/Developer — Automated resist track with programmable recipes; critical for reproducible EBL bilayer processing (bake temperature ±1°C, spin speed ±5 rpm at target).

- Striper — Post-etch resist removal. Combination of O₂ plasma ashing and wet solvent strip; critical to leave no organic residue. Downstream plasma strippers minimize ion bombardment damage to exposed device surfaces.

6) Characterization & Yield Management

6.1 In-Line Metrology

Rapid feedback is essential to maintain process control in quantum fabrication. Key measurements at each process step:

| Process Step | Measurement | Tool | Target / Tolerance |

|---|---|---|---|

| Film deposition | Thickness, resistivity, stress | Profilometer, four-point probe, wafer bow | ±2% thickness; RRR > 30 for Nb |

| Lithography | CD (critical dimension), overlay | SEM, optical microscope | CD ±5 nm (EBL); overlay < 0.5 µm (photo) |

| Etch | Etch depth, profile angle, roughness | Profilometer, SEM cross-section, AFM | < 1 nm RMS sidewall (photonics); 85–90° profile |

| Junction oxidation | Room-temperature resistance (Rₙ) | Probe station, parametric tester | Rₙ within ±5% of target across wafer |

6.2 Cryogenic Validation

Ultimate device performance can only be verified at millikelvin temperatures in a dilution refrigerator. Key figures of merit:

- T₁ (energy relaxation): > 50 µs for state-of-the-art transmons; limited by TLS, quasiparticles, and radiation

- T₂ (coherence time): > 100 µs (echo); limited by flux noise, charge noise, and TLS

- Q_i (internal quality factor): > 10⁶ for resonators at single-photon power; proxy for surface/interface loss

- Frequency targeting: Qubit frequency within ±50 MHz of design; avoids frequency collisions in multi-qubit chips

Establishing a fast turnaround between fabrication and cryogenic measurement (ideally < 1 week) is essential for process optimization. Many labs use dedicated test structures (resonators, single junctions) that can be measured before committing to full multi-qubit device runs.

7) Emerging Trends

7.1 Wafer-Scale Quantum Processing

As quantum processors scale beyond 100 qubits, the industry is shifting from chip-level to wafer-scale fabrication. This demands:

- 200 mm wafer compatibility for all process tools

- Junction Rₙ uniformity < ±3% across full wafer (current state-of-the-art: ±5–8%)

- Automated EBL with stitching error < 5 nm

- Integrated in-situ metrology (reflectometry, OES endpoint) for closed-loop process control

7.2 New Materials

- Tantalum (Ta): Emerging as a low-loss alternative to Nb for qubit capacitor pads; α-Ta (BCC) films show Q_i > 5 × 10⁶. Requires epitaxial growth on sapphire (heated substrate, UHV sputtering).

- TiN: Already used for high-Q resonators; grain boundary engineering (columnar vs. equiaxed) tunes kinetic inductance for parametric amplifiers.

- Granular aluminum (grAl): High kinetic inductance superinductor material for fluxonium qubits; deposited by e-beam evaporation in controlled O₂ partial pressure.

- 2D materials: Graphene Josephson junctions and hBN tunnel barriers offer gate-tunable superconducting elements; fabrication involves dry transfer stacking and EBL-defined contacts.

7.3 Atomic-Precision Processing

Atomic layer etching (ALE) and ALD enable monolayer-level control over film thickness and removal. For quantum devices, ALE of Al₂O₃ (trimming tunnel barrier thickness post-fabrication) and ALD of superconducting materials (TiN, NbN) are active research areas. See our Atomic Layer Etching Guide for process fundamentals.

8) Practical Recommendations

For Labs Starting Quantum Device Fabrication

- Prioritize substrate cleanliness. Invest in rigorous cleaning protocols (piranha, HF, solvent cascades) and in-situ plasma cleaning before deposition. Surface preparation has the highest ROI of any single process improvement.

- Establish dedicated chambers. Separate your superconductor etching/deposition chambers from any process involving Au, Cu, or magnetic materials. The cost of dedicated equipment is far less than the cost of debugging contamination-limited coherence.

- Start with resonators, not qubits. Coplanar waveguide resonators require only 1–2 lithography levels and provide direct feedback on material/interface quality (via Q_i) without needing a dilution refrigerator for every run (resonators can be characterized at 4 K in a dip probe).

- Control your oxidation. Josephson junction yield is dominated by oxidation uniformity. A dedicated oxidation chamber (or at minimum, a calibrated leak valve on your evaporator) with pressure gauge accuracy < 1 mTorr is essential.

- Build a process database. Record every parameter — base pressure, deposition rate, etch time, resist bake temperature — and correlate with device performance. Quantum device optimization is inherently statistical.

Equipment Checklist for a Quantum Fabrication Lab

| Category | Equipment | Priority | Quantum-Specific Requirements |

|---|---|---|---|

| Etching | ICP-RIE | Essential | Independent ICP/bias; load-lock; multi-gas (SF₆, Cl₂, BCl₃, Ar, O₂) |

| Etching | RIE | Essential | O₂ descum capability; precise low-power operation (10–50 W) |

| Etching | IBE/RIBE | Recommended | Tilt stage; in-situ SIMS or neutralizer; Ar + O₂ + reactive gases |

| Deposition | Magnetron Sputtering | Essential | UHV base pressure; DC + RF; multi-target; substrate heating |

| Deposition | PECVD | Essential | Stress-controlled SiO₂ and Si₃N₄; low-temperature recipes |

| Deposition | ALD | Recommended | Thermal ALD preferred; < 0.5% uniformity; Al₂O₃ and HfO₂ capability |

| Lithography | EBL | Essential | 100 kV; sub-10 nm resolution; precise dose control; alignment < 20 nm |

| Lithography | Mask Aligner / Stepper | Essential | i-line; overlay < 0.5 µm; backside alignment for flip-chip |

| Support | Plasma Cleaner | Essential | O₂/Ar selectable; low-power mode for gentle cleaning |

| Support | Coater / Developer | Essential | Programmable recipes; ±1°C bake; multi-layer resist capability |

| Support | Striper | Essential | Downstream O₂ plasma; low-damage mode |

Further Reading

- Reactive Ion Etching (RIE) – Principles, Applications, and Equipment Guide

- ICP-RIE Technology – Advanced High-Density Plasma Etching

- Magnetron Sputtering – Complete Guide

- PECVD – Complete Guide

- Atomic Layer Deposition (ALD) – Complete Guide

- Atomic Layer Etching (ALE) – Principles and Applications

- Process Chamber Materials & Contamination Control

- Lithography Process Integration Guide