HDP-CVD Applications: Gap Fill, STI, and Advanced Dielectric Deposition

By NineScrolls Engineering · 2026-03-10 · 14 min read · Materials Science

Target Readers: Process engineers, integration engineers, PIs, and equipment procurement teams working with dielectric deposition for semiconductor devices, MEMS, photonics, and advanced packaging. This guide assumes familiarity with basic CVD concepts — for foundational theory, see our HDP-CVD In-Depth Guide.

TL;DR Summary

High-Density Plasma Chemical Vapor Deposition (HDP-CVD) uniquely combines deposition and simultaneous sputtering to fill high-aspect-ratio gaps without voids — a capability that conventional PECVD and SACVD struggle to match below 0.25 µm geometries. The deposition/sputter ratio (D/S ratio) is the central process knob: higher bias power increases sputtering and prevents void formation, but excessive sputtering degrades throughput and damages underlying layers. This guide covers the gap-fill mechanism in detail, walks through STI and IMD/PMD applications, compares HDP-CVD with PECVD and SACVD quantitatively, and provides process optimization strategies for void-free dielectric fill.

1) The HDP-CVD Gap-Fill Mechanism

The defining feature of HDP-CVD is simultaneous deposition and sputtering — a process fundamentally different from conventional PECVD, where deposition and any etch steps must be sequential.

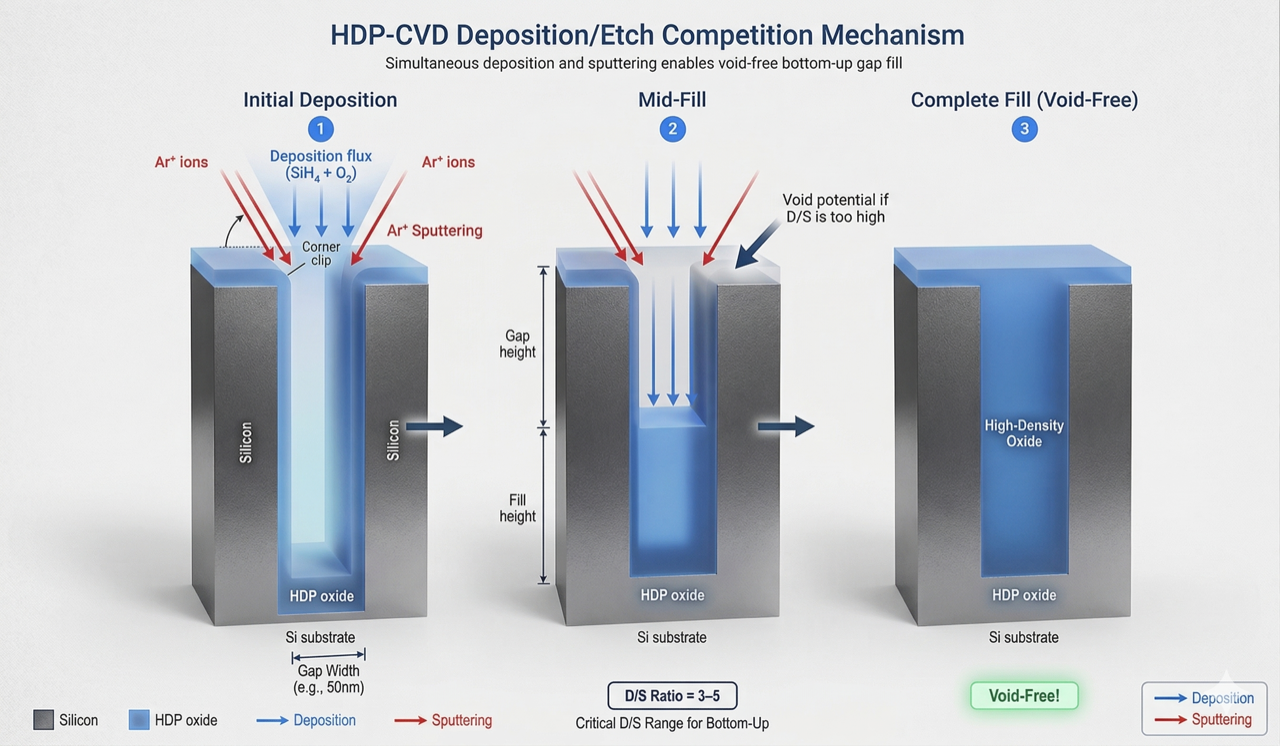

Figure 1: Simultaneous deposition/etch (D/E) competition mechanism — SiH₄/O₂ deposition flux fills from the bottom while Ar⁺ sputtering clips the top corners, preventing void formation through controlled D/S ratio optimization

1.1 Deposition/Etch Competition

In an HDP-CVD reactor, two RF power sources operate independently:

- Source power (ICP, 13.56 MHz): 1000–3000 W — generates the high-density plasma (10¹¹–10¹² cm⁻³) that dissociates SiH₄ and O₂ into film-forming radicals (SiH₃, SiH₂, O*)

- Bias power (substrate, 13.56 MHz): 300–1000 W — accelerates Ar⁺ ions toward the substrate for simultaneous sputtering of the deposited film

At every point on the wafer surface, the net film growth rate equals the deposition rate minus the sputter rate. On flat surfaces, deposition dominates and film grows normally. On the top corners of trenches and steps, the sputter yield is enhanced (faceting at ~45° sputtering angles), which prevents the "bread-loafing" overhang that causes voids in PECVD films.

1.2 The D/S Ratio

The deposition-to-sputter (D/S) ratio is the most important process parameter for gap fill:

- D/S > 5: Nearly pure deposition — behaves like PECVD, prone to void formation in high-AR gaps

- D/S = 3–5: Moderate sputtering — good for low-AR (<2:1) gap fill, highest throughput

- D/S = 2–3: Aggressive sputtering — required for AR > 3:1, slower net deposition rate

- D/S < 2: Excessive sputtering — net etch on some features, substrate damage risk, very low throughput

The D/S ratio is controlled by the bias-to-source power ratio. Increasing bias power (at constant source power) decreases the D/S ratio. On the NineScrolls HDP-CVD system, source power ranges from 1000–3000 W and bias power from 300–1000 W, providing D/S ratios from approximately 2 to 8 — covering the full application window.

1.3 Sputtering-Assisted Corner Removal

The key insight behind HDP-CVD gap fill is that sputter yield depends on the angle of incidence. At the top corners of a trench, incident Ar⁺ ions strike at near-optimal sputtering angles (~45°), removing material ~2–3× faster than on flat surfaces. This preferential corner sputtering keeps the trench opening wide as the fill progresses from the bottom up, preventing premature pinch-off and void formation.

The resulting trench fill profile shows characteristic triangular facets at the top corners — a visual signature of HDP-CVD that indicates healthy D/S ratio optimization.

2) Shallow Trench Isolation (STI) Fill

STI is the most demanding and highest-volume application for HDP-CVD. Every logic and memory chip manufactured at or below the 0.25 µm node uses STI for electrical isolation between transistors.

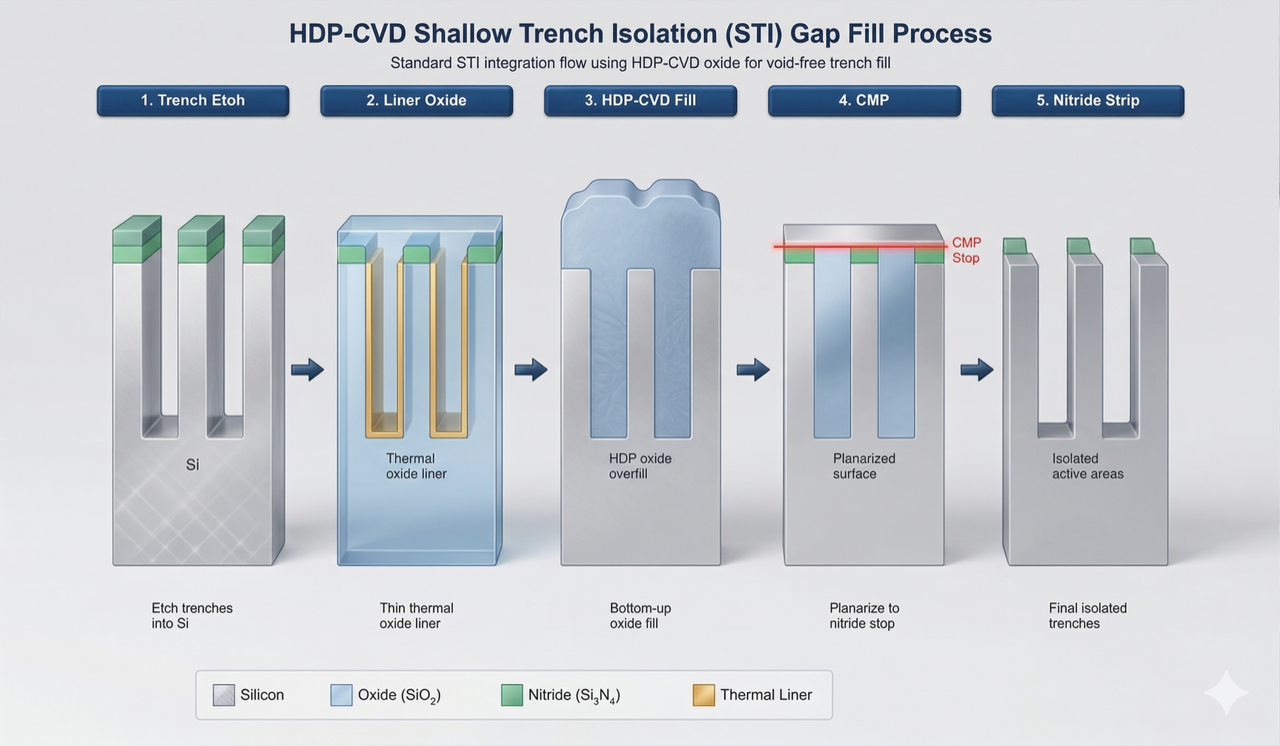

Figure 2: STI process flow — from trench etch through liner oxidation, HDP-CVD gap fill, CMP planarization, to final nitride strip, producing void-free oxide isolation between active device regions

2.1 STI Requirements

- Void-free fill: Trenches are typically 0.1–0.5 µm wide and 0.3–0.5 µm deep (AR = 1:1 to 5:1) — must fill completely without any voids

- Film quality: SiO₂ with wet etch rate ratio (WERR) <1.5× vs. thermal oxide — indicates dense, low-moisture film

- Uniformity: <3% thickness non-uniformity (1σ) across the wafer for consistent CMP removal

- Stress: Compressive stress in the range of −100 to −300 MPa is typical and acceptable for STI applications

- No pad nitride attack: The Si₃N₄ pad layer must survive the HDP-CVD deposition without thinning

2.2 Typical STI Fill Process Flow

- Pre-deposition clean: Brief Ar sputter clean (5–10 s at low bias) to remove native oxide and organic contamination from trench surfaces

- Liner deposition (optional): Thin thermal oxide or PECVD SiO₂ liner (5–10 nm) to improve interface quality

- HDP-CVD fill: SiH₄/O₂/Ar chemistry, D/S ratio ~3–4, stage temperature 20–100 °C, target overfill of 200–500 nm above trench top

- CMP planarization: Remove excess oxide and stop on the pad nitride

- Pad nitride strip: Hot phosphoric acid removes the Si₃N₄ pad

2.3 STI Process Window

| Parameter | Typical Range | Notes |

|---|---|---|

| Source Power | 2000–3000 W | Higher power → higher radical flux → faster deposition |

| Bias Power | 500–1000 W | Adjust to achieve D/S = 3–4 for AR ~3:1 |

| SiH₄ Flow | 30–80 sccm | Controls deposition rate — keep well below particle generation threshold |

| O₂ Flow | 50–150 sccm | O₂:SiH₄ ratio ~2:1 for stoichiometric SiO₂ |

| Ar Flow | 40–100 sccm | Sputter gas — higher flow enhances sputtering component |

| Pressure | 3–10 mTorr | Low pressure maintains high ion directionality |

| Stage Temperature | 20–100 °C | Higher temp improves film density but increases thermal budget |

| Dep Rate (net) | 150–400 nm/min | Net rate = deposition − sputtering |

3) Inter-Metal Dielectric (IMD) and Pre-Metal Dielectric (PMD)

Beyond STI, HDP-CVD is widely used for dielectric isolation layers in the interconnect stack.

3.1 PMD (Pre-Metal Dielectric)

PMD is deposited over the transistor contacts and before the first metal layer (M1). It must fill gaps between polysilicon gate stacks — which can have aspect ratios of 2:1 to 4:1 at advanced nodes — and provide a planar surface for contact patterning.

- Material: Undoped SiO₂ (USG) or phosphorus-doped SiO₂ (PSG, 2–4 wt% P) for gettering mobile ions

- Key requirement: Void-free fill between closely spaced gates, low moisture content, compatible with subsequent contact etch

- HDP-CVD advantage: Direct gap fill without the need for dep-etch-dep cycling

3.2 IMD (Inter-Metal Dielectric)

IMD is deposited between metal layers to provide electrical isolation. As metal line pitch decreases, the aspect ratio of the spaces between lines increases, demanding HDP-CVD gap-fill performance.

- Material: USG, FSG (fluorine-doped SiO₂, k ≈ 3.3–3.7), or SiON

- Key requirement: Void-free fill, low dielectric constant (to minimize RC delay), good adhesion to metal barrier layers

- Process consideration: Temperature must stay below 400–450 °C to avoid Al or Cu hillock formation

3.3 Doped Oxides — BSG, PSG, BPSG

The NineScrolls HDP-CVD system supports deposition of doped oxides through its 6-line gas system:

| Material | Dopant Gas | Dopant Concentration | Application |

|---|---|---|---|

| PSG | PH₃ (diluted in SiH₄ or N₂) | 2–8 wt% P₂O₅ | PMD passivation, mobile ion gettering |

| BSG | B₂H₆ (diluted) | 2–6 wt% B₂O₃ | Etch stop tuning, low-stress films |

| BPSG | B₂H₆ + PH₃ | 3–5 wt% B, 4–8 wt% P | Reflow planarization at 800–950 °C |

| FSG | SiF₄ or CF₄ | 2–6 at% F | Low-k IMD (k ≈ 3.3–3.7) |

4) HDP-CVD vs. PECVD vs. SACVD: Quantitative Comparison

Choosing the right deposition technique depends on the specific gap-fill requirements, thermal budget, throughput needs, and equipment availability. For a detailed discussion of PECVD capabilities, see our PECVD Complete Guide.

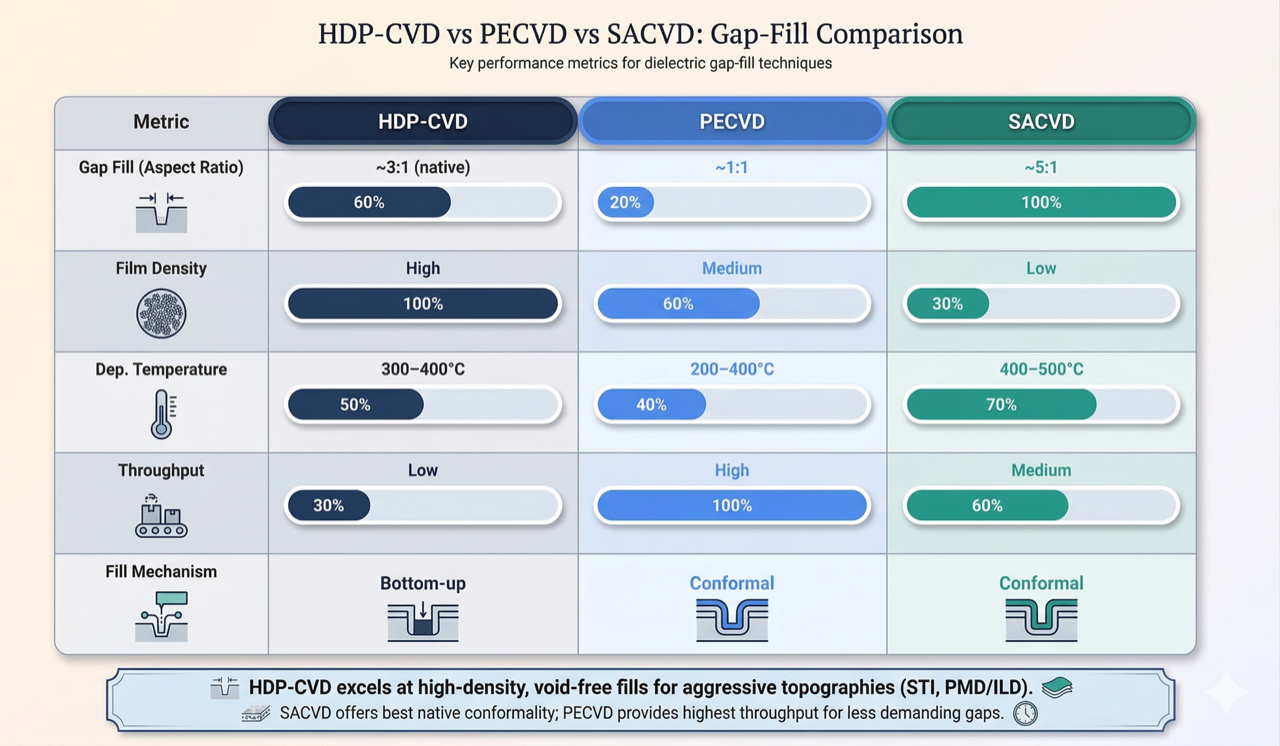

Figure 3: Quantitative comparison of three CVD gap-fill approaches — HDP-CVD excels in film density and bottom-up fill, PECVD offers highest throughput with conformal coverage, and SACVD achieves the highest aspect ratios with conformal deposition

| Parameter | HDP-CVD | PECVD | SACVD (O₃-TEOS) |

|---|---|---|---|

| Gap-Fill Capability | AR up to 6:1 (void-free) | AR up to 1.5:1 (void-free) | AR up to 3:1 (conformal) |

| Fill Mechanism | Bottom-up (dep + sputter) | Conformal drape | Surface-reaction limited (conformal) |

| Deposition Rate | 150–400 nm/min (net) | 100–500 nm/min | 50–200 nm/min |

| Film Density | 2.2–2.3 g/cm³ (near thermal) | 2.1–2.2 g/cm³ | 2.0–2.15 g/cm³ |

| WERR (vs. thermal SiO₂) | 1.1–1.5× | 1.5–3.0× | 2.0–4.0× |

| Temperature | 20–200 °C (NineScrolls) | 100–400 °C | 350–500 °C |

| Stress | Compressive (−100 to −300 MPa) | Tensile or compressive (tunable) | Tensile (+50 to +200 MPa) |

| Plasma Damage | Moderate (ion bombardment) | Low | Minimal (no plasma) |

| Equipment Cost | $$$ | $$ | $$ |

| Best For | STI, high-AR gap fill, dense dielectrics | Blanket films, passivation, MEMS | Conformal coating, moderate-AR fill |

When to Choose HDP-CVD Over PECVD

- Gap-fill required at AR > 1.5:1: PECVD will form voids; HDP-CVD fills cleanly

- Dense, high-quality oxide needed: HDP-CVD films approach thermal oxide quality

- CMP integration: The compressive stress and density of HDP-CVD films provide better CMP polish uniformity

- Moisture sensitivity: HDP-CVD produces drier films (lower Si-OH content) than PECVD

When PECVD is Sufficient

- Blanket deposition: Passivation layers, etch stops, anti-reflection coatings — no gap fill needed

- Material versatility: PECVD offers Si₃N₄, SiON, a-Si:H, DLC — materials HDP-CVD typically does not deposit

- Budget and footprint constraints: PECVD tools are simpler and less expensive

- Temperature-sensitive substrates: PECVD operates at lower temperatures and with less ion damage

5) Void-Free Fill Strategies

Achieving void-free fill is the primary challenge in HDP-CVD process development. Here are proven strategies for the most common gap-fill problems.

5.1 Dep-Etch-Dep (Multi-Step Fill)

For very high aspect ratios (AR > 4:1) or re-entrant profiles where even optimized single-step HDP-CVD forms weak spots, a multi-step dep-etch-dep process is effective:

- Partial fill (dep): Deposit 30–50% of the gap depth with standard D/S ratio

- Etch-back: Switch to pure Ar sputtering or NF₃ plasma etch to reopen the trench mouth by removing overhang

- Complete fill (dep): Resume deposition to fill the remaining gap

This multi-step approach can extend HDP-CVD gap-fill capability from AR ~4:1 to >6:1, at the cost of lower throughput (2–3× longer total process time).

5.2 Gas Chemistry Optimization

- SiH₄:O₂ ratio: Slightly oxygen-rich (O₂:SiH₄ = 1.8–2.2) produces stoichiometric SiO₂ with low particle generation. Excessive SiH₄ causes gas-phase nucleation (particles).

- Ar flow: Higher Ar flow increases the sputtering component for a given bias power. Adjust Ar flow as a fine-tuning knob for D/S ratio.

- He addition: Small He flows (5–20 sccm) improve backside cooling and thermal uniformity without significantly affecting the plasma chemistry.

5.3 Process Monitoring for Void Detection

- Cross-section SEM: The definitive method — cleave and image filled trenches. Perform after any process change.

- HF decoration: Brief dilute HF dip (10:1, 30 s) preferentially attacks voids and seams, making them visible under optical microscope

- Acoustic microscopy: Non-destructive void detection for production monitoring

- Film stress trending: Sudden stress changes can indicate fill quality degradation

6) Step Coverage Optimization

While HDP-CVD excels at gap fill, step coverage (the thickness ratio on vertical sidewalls vs. horizontal surfaces) requires attention for certain applications.

6.1 Step Coverage vs. Gap Fill

It is important to distinguish between these two concepts:

- Gap fill: The ability to fill a trench or gap without voids — HDP-CVD's primary strength

- Step coverage: The uniformity of film thickness on all surfaces (top, sidewall, bottom) — SACVD and ALD excel here

HDP-CVD typically produces 30–60% sidewall step coverage (vs. 80–100% for SACVD and >95% for ALD). For applications requiring conformal coating rather than gap fill (e.g., liner layers, conformal passivation), PECVD or SACVD may be the better choice.

6.2 Improving Step Coverage in HDP-CVD

- Increase pressure: Higher pressure (5–10 mTorr vs. 3–5 mTorr) increases the mean free path of scattering, directing more flux to sidewalls

- Reduce bias power: Less sputtering means less preferential removal from sidewalls

- Increase SiH₄ flow: Higher radical flux compensates for geometric shadowing

- Use TEOS as precursor: TEOS-based HDP-CVD provides better step coverage than SiH₄-based, though at lower deposition rate

7) Advanced Packaging Applications

HDP-CVD is increasingly used in advanced packaging for wafer-level packaging (WLP), through-silicon via (TSV) technology, and MEMS device passivation.

7.1 TSV Liner Deposition

Through-silicon vias (5–50 µm diameter, 50–300 µm deep, AR = 5:1 to 20:1) require conformal dielectric liners before Cu fill. While ALD provides the best conformality, HDP-CVD can deposit a thick oxide liner (200–500 nm) at the TSV bottom and upper sidewalls, which is sufficient for many packaging applications.

7.2 MEMS Cavity Fill and Seal

MEMS devices often require sealed cavities for pressure sensors, resonators, and gyroscopes. HDP-CVD can fill sacrificial trenches and seal small vent holes (<1 µm) through its simultaneous dep/sputter mechanism, providing hermetic sealing at relatively low temperatures (20–200 °C).

7.3 Redistribution Layer (RDL) Dielectric

In fan-out wafer-level packaging, HDP-CVD SiO₂ serves as an interlayer dielectric between redistribution metal layers. The dense, low-moisture film resists humidity penetration — important for the reliability of packaged devices.

7.4 Photonics Waveguide Cladding

Silicon photonics devices require thick SiO₂ cladding (1–3 µm) around waveguide structures with AR = 1:1 to 3:1. HDP-CVD fills the gaps between waveguides without voids while depositing dense oxide with refractive index close to thermal oxide (n ≈ 1.46 at 1550 nm).

8) Process Parameter Optimization

Systematic optimization of HDP-CVD processes follows a hierarchical approach — start with gap-fill quality, then optimize film properties, then tune for throughput.

8.1 Optimization Hierarchy

- Gap-fill quality (void-free): Adjust D/S ratio via bias power and Ar flow. Use cross-section SEM to verify.

- Film composition (stoichiometry): Tune SiH₄:O₂ ratio. Verify with FTIR (Si-O stretch at 1070 cm⁻¹, absence of Si-H at 2260 cm⁻¹).

- Film stress: Adjust bias power and temperature. Measure with wafer bow or thin-film stress tool.

- Uniformity: Optimize gas distribution (flow ratios per gas line), source power, and wafer position.

- Deposition rate (throughput): Increase source power and SiH₄ flow within the window established by steps 1–4.

8.2 Troubleshooting Common Issues

| Issue | Likely Cause | Corrective Action |

|---|---|---|

| Voids in gap fill | D/S ratio too high (insufficient sputtering) | Increase bias power or Ar flow; switch to dep-etch-dep for high AR |

| Particles on wafer | Gas-phase nucleation (excess SiH₄), or flaking from chamber walls | Reduce SiH₄ flow, run chamber clean with NF₃, replace shielding |

| High WERR (>2×) | Low film density (insufficient ion bombardment or temperature) | Increase bias power, increase stage temperature, verify O₂:SiH₄ ratio |

| Non-uniform thickness | Gas distribution imbalance, plasma non-uniformity | Balance gas line flows, check ICP coil condition, adjust wafer position |

| Substrate damage (charge, etch) | Excessive bias power, Ar flow too high | Reduce bias power, add He for cooling, consider SACVD for damage-sensitive layers |

| High film stress | Excessive ion bombardment, temperature mismatch | Reduce bias power, optimize temperature ramp, post-deposition anneal (if budget allows) |

8.3 NineScrolls HDP-CVD System Specifications

| Parameter | Specification |

|---|---|

| Source Power (ICP) | 1000–3000 W (13.56 MHz) |

| Bias Power | 300–1000 W (optional) |

| Stage Temperature | 20–200 °C |

| Gas System | 6-line (SiH₄, O₂, Ar, N₂, He, CF₄/NF₃) |

| Uniformity | <5% (1σ) |

| Footprint | 1.0 m × 1.5 m |

| Depositable Materials | SiO₂, Si₃N₄, SiON, SiC, Low-k, BSG/PSG/BPSG |

9) Frequently Asked Questions

What is the maximum aspect ratio HDP-CVD can fill without voids?

With a single-step process, HDP-CVD can reliably fill aspect ratios up to 4:1 in most geometries. With dep-etch-dep multi-step processing, void-free fill is achievable at AR up to 6:1 or even higher, depending on the trench profile (vertical sidewalls are easier than re-entrant profiles). Beyond 6:1, flowable CVD or ALD-based fill approaches become necessary. The NineScrolls HDP-CVD system supports both single-step and multi-step recipes, with the 6-line gas system enabling in-situ etch-back steps using NF₃ or CF₄.

Why does my HDP-CVD film have a higher wet etch rate than expected?

A high wet etch rate ratio (WERR) compared to thermal oxide indicates lower film density. Common causes: (1) Insufficient bias power — the sputtering/densification component is too low. Increase bias power in 50 W increments and re-measure. (2) Stage temperature too low — higher temperature promotes surface mobility of adatoms, producing denser films. Try 80–150 °C. (3) Non-stoichiometric composition — check O₂:SiH₄ flow ratio. Silicon-rich films (low O₂:SiH₄) have higher etch rates. (4) Excessive deposition rate — very high SiH₄ flows can outrun the densification mechanism. Reduce SiH₄ flow by 10–20% and verify. Target WERR <1.5× for STI-grade oxide.

Can HDP-CVD deposit silicon nitride?

Yes. HDP-CVD Si₃N₄ is deposited using SiH₄ and N₂ (or NH₃) as precursors with Ar as the sputtering gas. HDP-CVD nitride films are denser and have lower hydrogen content than PECVD nitride, making them suitable for etch stop layers and diffusion barriers. However, the deposition rate is lower than for SiO₂ (typically 50–150 nm/min net), and the higher ion bombardment during deposition can cause more substrate damage. For blanket nitride deposition where gap fill is not needed, PECVD is usually preferred for its higher throughput and lower damage. The NineScrolls HDP-CVD system supports Si₃N₄ deposition with its standard gas configuration.

How often does the HDP-CVD chamber need cleaning?

In-situ NF₃ plasma cleans should be run every 1–2 µm of accumulated deposition (typically every 3–5 production wafers, or after each run in an R&D environment). The clean removes deposited SiO₂ from the chamber walls and shielding. Full wet maintenance — including shield and dome replacement — is typically performed every 50–100 µm of accumulated deposition, or when particle counts exceed your specification. Key indicator: if particle counts on a monitor wafer start trending upward, increase the in-situ clean frequency before performing a full wet clean. Always run a conditioning deposition (1–2 µm on a dummy wafer) after any wet maintenance to re-passivate the chamber surfaces.

What is the advantage of HDP-CVD over SACVD for gap fill?

SACVD (sub-atmospheric CVD, typically O₃-TEOS) provides excellent conformal coverage but fills gaps by depositing a uniform coating on all surfaces — including the top corners. In high-AR trenches (>3:1), this conformal coating pinches off the trench opening before the bottom is filled, creating a void or weak seam. HDP-CVD fills bottom-up by simultaneously sputtering the top corners, keeping the opening wide. The result: HDP-CVD achieves void-free fill at higher ARs than SACVD. Additionally, HDP-CVD films are denser (WERR 1.1–1.5× vs. 2–4× for SACVD) and do not contain the moisture that O₃-TEOS films are known for. The tradeoff is that HDP-CVD involves ion bombardment, which can damage sensitive structures, and has higher equipment cost.

Is the bias power truly optional on the NineScrolls HDP-CVD?

Yes. The bias RF supply (300–1000 W) is optional and can be disabled entirely. Without bias, the system operates as a high-density plasma CVD without the sputtering component — essentially a high-density PECVD mode. This is useful for blanket deposition of dense films where gap fill is not needed, or for damage-sensitive substrates where any ion bombardment must be avoided. With bias enabled, you gain the full dep/sputter gap-fill capability. This dual-mode operation makes the NineScrolls HDP-CVD versatile for both gap-fill and blanket deposition applications in a single platform.

NineScrolls HDP-CVD — High-Density Plasma Chemical Vapor Deposition

The NineScrolls HDP-CVD delivers void-free gap fill up to 6:1 AR with independent source (1000–3000 W) and bias (300–1000 W) power control, 6-line gas system for SiO₂, Si₃N₄, SiON, SiC, doped oxides, and low-k materials, <5% uniformity, and a 1.0 × 1.5 m footprint. From STI fill to advanced packaging — one platform, full flexibility.